# S5: Combining white-box countermeasures to resist state-of-the-art attacks

Alex Charlès<sup>1</sup> and Aleksei Udovenko<sup>2</sup>

<sup>1</sup> DCS, University of Luxembourg, Esch-sur-Alzette, Luxembourg

[alex.charles@uni.lu](mailto:alex.charles@uni.lu)

<sup>2</sup> SnT, University of Luxembourg, Esch-sur-Alzette, Luxembourg

[aleksei@affine.group](mailto:aleksei@affine.group)

**Abstract.** In white-box cryptography, the DCA attack broke early encoding-based countermeasures, leading to the utilization of masking schemes against a surge of automated attacks. The recent filtering attack from CHES 2024 broke the last viable masking scheme from CHES 2021, which resisted both computational and algebraic attacks, raising the need for new countermeasures.

In this work, we propose two countermeasures in the white-box setting by performing the first formal study of the combinations of existing countermeasures and demonstrating that applying Dummy Shuffling (EUROCRYPT 2021) then ISW masking (CRYPTO 2003) to a circuit carries algebraic, correlation, and filtering security - necessary conditions to withstand state-of-the-art automated attacks. We also show that applying these two countermeasures in the opposite order leads to a rather strong higher-order filtering (HOF) attack, highlighting the importance of the order of application of the combined countermeasures.

We also propose a new masking scheme called *S5*, standing for Semi-Shuffled Secret Sharing Scheme, a scheme merging Dummy Shuffling and ISW in a single countermeasure more efficiently than a direct composition.

**Keywords:** White-box Cryptography · S5 · ISW · Dummy Shuffling · HDDA · FLDA · HODCA

## 1 Introduction

In 1999, Kocher, Jaffe, and Jun [KJJ99] showed that an implementation can be vulnerable if there is a leak of its side-channel information, such as electrical power consumption or timing of the execution, which startled the development of the side-channel field. Later, in 2002, Chow, Eisen, Johnson, and van Oorschot [CEJv02, CEJv03] broadened the question by supposing that an attacker could fully access the implementation during the computation, which they called white-box. For example, a white-box attacker observing the intermediate values can find the state before and after adding the key and easily recover it. Therefore, the authors proposed to encode the intermediate values of the ciphers and perform computations through a set of lookup tables. These tables typically represent three consecutive operations composed in one unit: decode the encoded input, perform operations, and re-encode the output. While the attacker knows the lookup tables in the white-box context, the idea of [CEJv02] was that decomposing the tables would be difficult. Different encoding designs were proposed [XL09, Kar11], but all were broken with a variety of attacks [BGEC04, DRP13, LRD<sup>+</sup>14].

In 2016, Bos, Hubain, Michiels, and Teuwen [BHMT16] showed that a white-box adaptation of the *differential power analysis* from [KJJ99], which they called *differential computational analysis* (DCA), can be applied to breaking encoding-based white-box

implementations (studied consequently in more detail in [ABMT18, RW19a]), without any adaptation to the encoding design. Traditional side-channel masking schemes such as ISW [ISW03] thwart this attack. Consequently, [BU18, GPRW20] presented a new automated attack, *linear decoding analysis* (LDA), that can efficiently break linear masking schemes in the white-box context. In particular, it has been used during the WhibOx 2017 contest to break the winning white-box implementation of the AES [GPRW17].

To prevent the LDA attack, Biryukov and Udovenko proposed the first nonlinear masking scheme [BU18], and another countermeasure called *Dummy Shuffling* [BU21]. Although these countermeasures alone are susceptible to the DCA attack, it was suggested that they can be combined with a correlation-resistant scheme like ISW. The combination would resist in theory both DCA and LDA by forcing the two attacks to use higher-order/degree variants (HODCA [BRVW19], HDDA [GPRW20]) which have an exponential cost on their order/degree. However, they did not provide details on how such a combination should be performed or provide a security analysis of the result.

Seker, Eisenbarth, and Liskiewicz [SEL21] proposed a masking scheme (*SEL*) of degree up to three, generalizing the quadratic scheme from [BU18] and making it much lighter. Optimizations of higher-order/degree attacks were found [GRW20, TGCX23], while remaining slow for high-degree instances of the SEL masking scheme. However, recently, Charlès and Udovenko showed that all instances of this scheme are weak to LPN-based attacks [CU23] and *filtered linear decoding analysis* (FLDA) [CU24], making this scheme insecure on its own.

**Our contribution** The break of the SEL masking scheme by filtering attacks left no viable countermeasure. Therefore, in this study, we extend the work of [BU21] from EUROCRYPT 2021, by proposing a first formal study of the combinations of the two main countermeasures - ISW masking scheme and dummy shuffling - and a new, more efficient scheme called *S5*, resisting the main automated white-box attacks in the literature.

1. *(ISW and Dummy Shuffling Combination)* ISW and Dummy shuffling achieve correlation and algebraic resistances respectively, and we demonstrate that applying both countermeasures sequentially to a circuit carries both resistances and withstand state-of-the-art attacks. Furthermore, we point out the importance of the order of application of countermeasures, as applying ISW then Dummy Shuffling results in a different circuit structure from the reverse order, with different implementation sizes and security levels.

2. *(Higher-Order filtering)* We show that performing ISW then Dummy Shuffling is susceptible to a Higher-Order Filtering attack of complexity lower than expected, while the other order of application is more resistant. This contradicts the earlier belief that the combination order is not important.

3. *(Semi-Shuffled Secret-Sharing Scheme)* To lower the implementation cost of Dummy shuffling composed with ISW while having equivalent security properties, we propose *S5*, a new countermeasure extending the AND gadget of ISW by splitting the information of only one of its shares among different slots, using a structure similar to Dummy Shuffling.

4. *(Benchmarks)* We provide theoretical estimations and experimental benchmarks for the gate costs of all three combined countermeasures. The supporting code implementing *S5* and benchmarks is available at:

[github.com/S5white-box/code](https://github.com/S5white-box/code)

5. *(Security proofs)* Finally, we extend the algebraic proof from [BU21] to *S5* and the two combinations of countermeasures, prove Strong Non-Interference (SNI) [BBD<sup>+</sup>16] of the *S5* gadget, and verify it up to 14 shares using the MaskVerif tool [BBC<sup>+</sup>19].

## 2 Notations and definitions

- The binary field is denoted by  $\mathbb{F}_2$  and the vector space of dimension  $n$  over  $\mathbb{F}_2$  is denoted by  $\mathbb{F}_2^n$ .

- For a vector  $v \in \mathbb{F}_2^n$  (resp. a list  $L$  of  $n$  elements), we denote its  $i^{th}$  element,  $1 \leq i \leq n$ , by  $v_i$  (resp.  $L_i$ ), such that  $v = (v_1, \dots, v_n)$  (resp.  $L = (L_1, \dots, L_n)$ ).

- We denote the addition in this binary field by “ $\oplus$ ”, also called XOR, and we keep these notations when adding two vectors of  $\mathbb{F}_2^n$ .

- Similarly, we denote the multiplication in  $\mathbb{F}_2$  by “ $\cdot$ ”, also called AND, and we extend these notations to multiply two vectors from  $\mathbb{F}_2^n$  coordinate-wise.

- $m$  vectors from  $n\mathbb{F}_2^n$  (resp. lists of  $n$  elements) can be arranged in a  $n \times m$  matrix (resp. two-dimensional list)  $M$ . The element of  $M$  of the  $i^{th}$ ,  $i \in (1, \dots, n)$ , row and the  $j^{th}$ ,  $j \in (1, \dots, m)$ , column is denoted by  $M_{i,j}$ .

- We denote the number of elements in a given list, vector, or set  $X$  by  $|X|$ .

- For a Boolean function  $f$ , we denote its weight (the number of preimages of 1) by  $|f|$ .

- We denote the matrix multiplication exponent by  $\omega$ , which depends on the algorithm employed:  $\omega \approx 2.8$  for the Strassen algorithm [Str69].

- A fresh randomness is denoted by  $\$$ , and is computed by a pseudo-random number generator in the white-box setting, which is outside of the scope of this paper. A variable  $v$  receiving a fresh random value is denoted by  $v \leftarrow \$$ .

## 3 The framework

White-box model includes all the attacks from side-channel cryptography, which we can divide into non-invasive and invasive. The first group, introduced in [Koc96], consists of observing the side-channel information, such as the electromagnetic field or power consumption of a hardware component, without interfering with its process. The second group consists of actively injecting errors with, for instance, a laser beam or a voltage glitch in the computation to observe its impact [BS97, BBB<sup>+</sup>22].

In the white-box cryptography setting, the side-channel attacks become easier to mount, as an attacker has direct access to the software. So, instead of measurements that vary in values and time, the value of each variable is available without any measurement noise. Similarly, for invasive attacks, injecting a fault can be done with bit precision and without failed attempts [SMdH15, AT20]. Furthermore, an attacker can perform deeper software analysis to optimize the previously exposed attacks [GRW20, TGCX23].

Designing a white-box implementation would require preventing all of these attacks, while thwarting even one is already an open question. For this reason, we will only consider non-invasive attacks that are not based on software analysis, since the only viable protection against these presented in [SEL21] was recently broken by a polynomial time attack [CU24].

### 3.1 Preliminaries

**Circuits and masking schemes** Any stateless implementation can be represented as a *Boolean circuit*, a representation using only bit variables that are related to each other with bitwise gates (AND, XOR and NOT), that a masking scheme can transform. A masking

scheme encodes each bit variable  $v$  into  $n > 1$  *shares* using an *encoding function*, such that the corresponding *decoding function* applied to these  $n$  bit variables retrieves the original bit variable  $v$ . Each of these  $n$  shares carries partial information of  $v$ , forcing an attacker to analyze multiple shares to retrieve full information of  $v$ .

To perform a bitwise gate without having to decode the  $n$  input shares (of each input) and thus leaking information on  $v$ , the gates are replaced by *gadgets*, performing operations without leaking information and outputting the shares of the resulting variable. For instance, instead of having  $\text{XOR}(x, y) = z = x \oplus y$ , we would have the shares  $(x_1, \dots, x_n)$  and  $(y_1, \dots, y_n)$  as input such that  $\text{Decode}(x_1, \dots, x_n) = x$  and  $\text{Decode}(y_1, \dots, y_n) = y$ , and we would replace the XOR by its gadget  $\text{GadgetXOR}((x_1, \dots, x_n), (y_1, \dots, y_n)) = (z_1, \dots, z_n)$  satisfying  $\text{Decode}((z_1, \dots, z_n)) = z = x \oplus y$ .

In the next subsections, we show that the decoding function often XORS shares together to resist correlation attacks, and can perform other methods to resist algebraic attacks, which leads to the following definition:

**Definition 1.** Let  $\mathcal{D} : \mathbb{F}_2^n \mapsto \mathbb{F}_2$  be a decoding function of a masking scheme  $\mathcal{M}$  and  $v$  a bit variable represented by  $n$  shares.  $\mathcal{D}$  can be expressed as  $\mathcal{D}(v) = L(v_1, \dots, v_a) \oplus N(v_{a+1}, \dots, v_n)$ , with linear  $L : \mathbb{F}_2^a \rightarrow \mathbb{F}_2$ ,  $a \leq n$ , and nonlinear  $N : \mathbb{F}_2^{n-a} \rightarrow \mathbb{F}_2$ . We call  $L$  the *linear part* of  $\mathcal{M}$  and  $N$  the *nonlinear part* of  $\mathcal{M}$ .

**Example 1.** The BU masking scheme (c.f. Subsection 3.3) has decoding function  $D(x_1, x_2, x_3) = x_1 \oplus x_2 \cdot x_3$ . The linear part of BU is  $x_1$ , and its nonlinear part is  $x_2 \cdot x_3$ .

**Example 2.** The ISW $_\ell$  masking scheme (c.f. Subsection 3.3) has decoding function  $D(x_1, \dots, x_\ell) = x_1 \oplus \dots \oplus x_\ell$ . The linear part of ISW $_\ell$  is  $D$  entirely and it has no nonlinear part.

**Definition 2.** Let  $\mathcal{D} : \mathbb{F}_2^n \mapsto \mathbb{F}_2$  be the decoding function of a masking scheme with  $n$  shares, and let  $\mathcal{L}$  be the set of linear functions mapping  $\mathbb{F}_2^n$  to  $\mathbb{F}_2$ . The *noise rate* of the masking scheme is given by:

$$\tau = \min_{f \in \mathcal{L}} \left( \frac{\sum_{x \in \mathbb{F}_2^n} [\mathcal{D}(x) \oplus f(x)]}{2^n} \right),$$

where the sum in the numerator is over the integers.

**Example 3.** The BU masking scheme (c.f. Subsection 3.3) has decoding function  $D(x_1, x_2, x_3) = x_1 \oplus x_2 \cdot x_3$ . Choosing the linear function  $f(x_1, x_2, x_3) = x_1$  shows that its noise rate is  $\tau = \frac{1}{4}$ .

**Traces** Our study focuses on masking schemes mainly designed to resist (extended) grey-box attacks in the white-box model. These attacks are fully automated and only require as input the *computational traces* of the implementation. In the side-channel model also called the grey-box model, a trace is the side-channel information leaked during the ciphering of a plaintext. In the white-box setting, since we have full access to the implementation, we have direct access to the bit values used to perform the encryption, without any measurement noise.

We can record every bit value computed by every bitwise gate to generate traces over different inputs. These bitwise gates are called *nodes*. Over  $T$  plaintexts, a *node* will take  $T$  different values in  $(0, 1)$ , which gives a vector of dimension  $T$  over  $\mathbb{F}_2$ , called the *node vector*. We can arrange all of the  $N$  node vectors  $V_i \in \mathbb{F}_2^T$ ,  $i \in (1, \dots, N)$  in a  $T \times N$

matrix over  $\mathbb{F}_2$  as follows:

$$\begin{array}{ccccc}

& \text{node 1} & \text{node 2} & \cdots & \text{node } N \\

\text{trace 1} & V_{1,1} & V_{1,2} & \cdots & V_{1,N} \\

\text{trace 2} & V_{2,1} & V_{2,2} & \cdots & V_{2,N} \\

\vdots & \vdots & \vdots & \vdots & \vdots \\

\text{trace } T & V_{T,1} & V_{T,2} & \cdots & V_{T,N}

\end{array}$$

**Selection function** In combination with the traces, a selection function is needed to perform a grey-box attack. In the case of the AES, an attack often recovers the key byte by byte. Since the input and the AES Sbox are known, it is possible to brute-force the 256 key byte possibilities and deduce for each of them (say) the first bit of the output of the AES Sbox of the first round. For another input, we can compute 256 new values for each possibility of the key bytes. Over  $T$  traces, we obtain 256 vectors in  $\mathbb{F}_2^T$  per key byte, denoted by *node vectors*. The set of selection vectors is denoted by  $\mathcal{K}$ . For the AES, we have  $|\mathcal{K}| = 4096^1$ .

Consider an unprotected circuit of an AES implementation. One of its nodes will correspond to the first bit of the output of the first Sbox of the first round. With enough traces and a selection function, it is possible to distinguish one of the node vectors corresponding exactly to one of the selection vectors. With enough traces, we can be sure that the suggested key byte is the correct guess. This simple attack, called exact matching, explains the base principle of the grey-box attacks, but is not enough to break protected circuits.

### 3.2 Grey-box attacks in the white-box context

**Differential Computational Analysis (DCA)** The first white-box implementations [CEJv02, CEJv03] used nibble (4-bit) encodings as a countermeasure, making the involved node vectors different from the selection vectors. However, [BHMT16] showed in their *Differential Computational Analysis* attack (DCA) that some of the node vectors correlate with the correct selection vectors despite the encodings [SMG16, RW19b, CH24]. By computing the correlation of each of the node vectors with the selection vectors, Bos *et al.* showed that the highest absolute correlation score achieved by the selection vector among the 256 guesses of a key byte correspond to the correct guess, with enough traces.

*To prevent a correlation attack, a countermeasure should have a non-empty linear part.*

**Linear Decoding Analysis (LDA)** To thwart correlation attacks, linear masking schemes have been employed, which force an attacker to find a subset of node vectors that XORS to one of the selection vectors to retrieve the corresponding key byte. In [GPRW18], the authors pointed out that we can perform linear algebra in the white-box context since we have information on the traces without any noise. Therefore, an attacker can try to observe if one of the selection vectors is a solution of a linear equation from all the node vectors. However, solving a linear equation over all the node vectors would often require impractical amounts of time and memory, so we need to attack subsets of nodes.

A simple method to attack relevant subsets is a *sliding window*, which consists of taking the  $\mathcal{W}$  consecutive node vectors ( $\mathcal{W}$  is called *the window size*), performing the attack, and sliding forward by  $\mathcal{S} \leq \mathcal{W}$  nodes, to take the  $\mathcal{S} + 1, \dots, \mathcal{S} + \mathcal{W}$  next nodes, and so on. In this work, all the attack complexities will be given in function of the subset size, denoted by  $\mathcal{W}$  for this reason. Other techniques to choose more efficient subsets also exist [GRW20, TGCX23], but are considered software analysis and are out of the scope of this

---

<sup>1</sup>It is often beneficial to consider more selection functions, such as other outputs of the S-box or their linear combinations. For illustration purposes, we only consider the minimal such set.

paper.

*To prevent an algebraic attack, a countermeasure should have a non-empty nonlinear part.*

**Higher Order attacks (HDDA, HODCA)** Some nonlinear masking schemes were employed to prevent such algebraic attacks. Still, it is possible to perform a Higher-Order version of the DCA attack (HODCA) [BRVW19] against correlation-resistant schemes, and a Higher-Degree version of the LDA attack (HDDA) [GPRW20] against masking schemes algebraic-resistant schemes. Both these techniques use the same idea of extending the window by appending all the combinations of XOR (resp. AND) of node vectors before performing DCA (resp. LDA). This extension of the window adds  $\sum_{i=2}^{\mathcal{O}} \binom{\mathcal{W}}{i}$  new vectors, with  $\mathcal{O}$  the order or the degree, which is equivalent to an exponential in  $\mathcal{O}$  increase. Therefore, these attacks are exponential in their order or degree.

*To prevent higher-order attacks, a countermeasure should have tunable parameters.*

**White-Box Learning Parity With Noise (WBLPN)** This attack presented in [CU23] showed that performing a grey-box attack in the white-box setting could be considered as solving a Learning Parity with Noise (LPN) problem. The LPN problem consists of solving linear equations in the presence of noise. In the white-box setting, we can consider that the nonlinear part of a masking scheme is a noise occurring following the noise rate  $\tau$  probability. This attack is exponential in  $\mathcal{W}$ , but the lower  $\tau$  is, the more efficient the attack becomes and can compete with the higher-order ones.

*To prevent WBLPN attacks, the noise rate of a countermeasure should not be low.*

**Filtering attacks (FLDA, HOF)** In [CU24], a new class of attacks called *filtering* was proposed, which nullifies one share by choosing the subset of traces where the node corresponding to the share is equal to zero. This methodology is very efficient against masking schemes that have a nonlinear part consisting of a few monomials of high degrees, as nullifying one of the shares of a monomial nullifies the whole nonlinear monomial ( $x_1 \cdot x_2 \cdot x_3$  becomes equal to zero if we force one of the three variables to be equal to zero). The authors also proposed Higher-Order Filtering (HOF) for future countermeasure designs, which nullifies multiple shares simultaneously. This will inspire as a useful attack in the following sections.

*To prevent Filtering attacks, the countermeasure security should not be tampered with a low order of filtering.*

To summarize, Table 1 shows all the available attacks and their best time and space complexities in the literature.

**Table 1:** Time and space complexities of grey-box attacks in the white-box context onto a subset of nodes of size  $\mathcal{W}$ .  $\omega$  is the matrix multiplication exponent,  $|\mathcal{K}|$  is the number of selection vectors (4096 for the AES),  $\tau$  is the noise rate of the countermeasure,  $k_\tau$  (resp.  $T_{\mathcal{O},\tau}$ ) is a constant that depends on  $\tau$  (resp.  $\mathcal{O}$  and  $\tau$ ),  $c_\tau = \frac{1}{1-\tau}$ ,  $c'_\tau = \frac{-\ln(1-\tau)}{(1/2)-\tau}$ .

| Attack                      | Reference      | Time, $O(\cdot)$                                                              | Traces, $O(\cdot)$           |

|-----------------------------|----------------|-------------------------------------------------------------------------------|------------------------------|

| DCA $_\tau$                 | [BHMT16]       | $\mathcal{W}k_\tau \mathcal{K} $                                              | $k_\tau$                     |

| LDA                         | [GPRW18, CU24] | $\mathcal{W}^\omega +  \mathcal{K} \mathcal{W}$                               | $\mathcal{W}$                |

| HODCA $_{\mathcal{O},\tau}$ | [BRVW19]       | $\mathcal{W}^{\mathcal{O}} \mathcal{K} T_{\mathcal{O},\tau}$                  | $T_{\mathcal{O},\tau}$       |

| HDDA $_d$                   | [GPRW20, CU24] | $\mathcal{W}^{d\omega} +  \mathcal{K} \mathcal{W}^d$                          | $\mathcal{W}^d$              |

| WBLPN $_\tau$               | [CU23]         | $\mathcal{W}^{\omega-1} \mathcal{K} c'_\tau c_\tau^{\mathcal{W}}$             | $\mathcal{W}c'_d$            |

| FLDA                        | [CU24]         | $\mathcal{W}^{\omega+1} +  \mathcal{K} \mathcal{W}^2$                         | $2\mathcal{W}$               |

| HOF $_{\mathcal{O}}$ -LDA   | [CU24]         | $\mathcal{W}^{\omega+\mathcal{O}} +  \mathcal{K} \mathcal{W}^{\mathcal{O}+1}$ | $2^{\mathcal{O}}\mathcal{W}$ |

### 3.3 Masking schemes

**ISW masking scheme** A well-known solution against correlation attacks has been proposed in [ISW03] for the grey-box context: replacing every bit variable  $v$  by  $\ell$  random shares  $(x_1, \dots, x_\ell)$ , such that  $v = \bigoplus_{i=1}^\ell x_i$ . That way, each node vector corresponding to the shares does not correlate with any selection vectors.

While the XOR gadget consists of XORing the shares coordinate-wise ( $z_i = x_i \oplus y_i$  for  $i \in (1, \dots, \ell)$ ), the AND gadget is more complex: an SNI version of it is given in Algorithm 1, taken from [BBG<sup>+</sup>16].

---

#### Algorithm 1 SecMult

---

**Inputs:**

- $(x_1, \dots, x_\ell)$  s.t.  $\bigoplus_{i=1}^\ell x_i = x$

- $(y_1, \dots, y_\ell)$  s.t.  $\bigoplus_{i=1}^\ell y_i = y$

- $\frac{(\ell-1)\ell}{2}$  fresh random bits

**Output:**  $(z_1, \dots, z_\ell)$  s.t.  $\bigoplus_{i=1}^\ell z_i = x \cdot y$

```

1: for  $i \in (1, \dots, \ell)$  do

2:    $z_i \leftarrow x_i \cdot y_i$

3: end for

4: for  $i \in (1, \dots, \ell)$  do

5:   for  $j \in ((i+1), \dots, \ell)$  do

6:      $r \leftarrow \$$

7:      $z_i \leftarrow z_i \oplus r$

8:      $z_j \leftarrow z_j \oplus ((r \oplus (x_i \cdot y_j)) \oplus (x_j \cdot y_i))$

9:   end for

10: end for

11: return  $z$

```

---

This AND gadget, SecMult, can be represented by a matrix storing intermediate computations in its cells, and yielding XOR of each of its rows as a share of the result.

**Example 4.** Let  $\ell = 3$ . We receive  $(x_1, x_2, x_3)$  and  $(y_1, y_2, y_3)$  such that  $x_1 \oplus x_2 \oplus x_3 = x$  and  $y_1 \oplus y_2 \oplus y_3 = y$ , and we want to compute  $(z_1, z_2, z_3)$  such that  $z_1 \oplus z_2 \oplus z_3 = x \cdot y$ . We have:

$$x \cdot y = (x_1 \oplus x_2 \oplus x_3) \cdot (y_1 \oplus y_2 \oplus y_3) = \quad (1)$$

$$x_1 \cdot y_1 \quad (1)$$

$$\oplus x_2 \cdot y_1 \oplus x_2 \cdot y_2 \oplus x_1 \cdot y_2 \quad (2)$$

$$\oplus x_3 \cdot y_1 \oplus x_3 \cdot y_2 \oplus x_3 \cdot y_3 \oplus x_2 \cdot y_3 \oplus x_2 \cdot y_3 \oplus x_1 \cdot y_3 \quad (3)$$

Here, the first line of the equation will correspond to the first line of the matrix, the second to the second, and the third to the third. To ensure SNI security of the gadget (c.f. Section 6, [BBG<sup>+</sup>16]),  $\frac{(\ell-1)\ell}{2} = 3$  fresh random bits  $(r_{1,2}, r_{1,3}, r_{2,3})$  are involved, as explained in Algorithm 1, which gives the following matrix:

$$\begin{aligned} z_1 &\leftarrow \begin{pmatrix} x_1 \cdot y_1 & r_{1,2} & r_{1,3} \\ x_2 \cdot y_1 \oplus r_{1,2} \oplus x_1 \cdot y_2 & x_2 \cdot y_2 & r_{2,3} \\ x_1 \cdot y_3 \oplus r_{1,3} \oplus x_3 \cdot y_1 & x_2 \cdot y_3 \oplus r_{2,3} \oplus x_3 \cdot y_2 & x_3 \cdot y_3 \end{pmatrix} \\ z_2 &\leftarrow \begin{pmatrix} x_1 \cdot y_1 & r_{1,2} & r_{1,3} \\ x_2 \cdot y_1 \oplus r_{1,2} \oplus x_1 \cdot y_2 & x_2 \cdot y_2 & r_{2,3} \\ x_1 \cdot y_3 \oplus r_{1,3} \oplus x_3 \cdot y_1 & x_2 \cdot y_3 \oplus r_{2,3} \oplus x_3 \cdot y_2 & x_3 \cdot y_3 \end{pmatrix} \\ z_3 &\leftarrow \begin{pmatrix} x_1 \cdot y_1 & r_{1,2} & r_{1,3} \\ x_2 \cdot y_1 \oplus r_{1,2} \oplus x_1 \cdot y_2 & x_2 \cdot y_2 & r_{2,3} \\ x_1 \cdot y_3 \oplus r_{1,3} \oplus x_3 \cdot y_1 & x_2 \cdot y_3 \oplus r_{2,3} \oplus x_3 \cdot y_2 & x_3 \cdot y_3 \end{pmatrix} \end{aligned}$$

Now, each  $z_i, i \in (1, 2, 3)$ , gets the XOR of the elements of the  $i^{th}$  line of the matrix. We can observe that  $z_1 \oplus z_2 \oplus z_3$  contains every element of the previous equation, and two occurrences of each fresh randomness which cancels out and is, therefore, equal to  $x \cdot y$ .

**BU masking scheme** To thwart the Linear Decoding Analysis (LDA) attack that breaks ISW, a nonlinear masking scheme was proposed in [BU18], achieving algebraic security. This masking scheme shares every bit variable  $v$  by three shares  $x_1, x_2, x_3$  such that  $v = x_1 \oplus x_2 \cdot x_3$ . However, contrarily to ISW, this scheme would not resist correlation attacks as  $x_1$  correlates with  $v$ . Although the authors hypothesized that, once combined with a correlation-resistant scheme such as the ISW masking scheme, the resulting circuit would resist both correlation and algebraic attacks, no formal claim or study was done since then.

**SEL masking scheme** A first masking scheme resisting both algebraic and correlation attacks was proposed in [SEL21], which has decoding function:  $v = \bigoplus_{i=1}^{\ell} x_i \oplus \prod_{i=1}^d \tilde{x}_i$ . The  $x_i$  are the linear shares and bring correlation resistance as for the ISW masking scheme, forcing HODCA to order  $\ell$ , while the  $\tilde{x}_i$  bring algebraic resistance as for BU masking scheme, forcing HDDA to be of degree  $d$ . Since these two attacks are exponential in their order/degree, this masking scheme was enough to thwart them if  $\ell$  and  $d$  were chosen big enough. However, it was later shown that filtering attacks [CU24] could break it in polynomial time.

### 3.4 The dummy shuffling countermeasure

In [BU21], the authors showed that the shuffling methodology used to increase measurement noise in the grey-box model (*c.f.* [HOM06, VMKS12]) could be adapted in the white-box model to prevent algebraic attacks, by creating  $s$  exact copies of the implementation to protect, called *slots*. At each execution, one of the slots is chosen at random to perform the real computation (*the main slot*) and is given the real input, while the  $s - 1$  others are given random inputs (*the dummy slots*). The shuffling *flags* are derived pseudorandomly from the input to choose which slot will be the main. For  $s$  slots, every bit input is passed through the input-shuffling function with  $s - 1$  random bits of the dummy slots, which permutes them given the flags. Each slot then computes the function on its input, resulting in  $s$  outputs. Finally, the  $s$  output bits are passed through the output-selection function to recover the main slot output, which unshuffles them given the shuffling flags.

**Definition 3.** Let  $f$  be the flags of a Dummy Shuffling implementation, and  $L$  a list of  $n > 1$  elements:

- We define a function that shuffles a list  $L$  of  $n > 1$  elements by  $\text{Shuffle}_f(L)$ .

- Similarly, we define a function that unshuffles a list  $L$  of  $n > 1$  elements by  $\text{Unshuffle}_f(L)$ .

- We have  $\text{Shuffle}_f \circ \text{Unshuffle}_f(L) = \text{Unshuffle}_f \circ \text{Shuffle}_f(L) = L$ .

- We denote the function that returns the element of the main slot of a shuffled list  $L$  by  $\text{DecodeDS}_f(L)$ .

Applying the *Shuffle* function with the flags  $f$  to a list containing zero followed by random values creates *pre-shuffled randomness*. For each AND gate, a *pre-shuffled randomness* is created and XORed to refresh them to ensure algebraic security. The Dummy Shuffling Refresh function is depicted in [Algorithm 2](#), given the flags  $f$ .

**Definition 4.** A dummy shuffling implementation is performed over three main phases:

1. **Input-encoding:** This first phase of the implementation chooses the flags  $f$  randomly from the input, uses it to generate every pre-shuffled randomness that will be needed during the second phase and encodes every input of the algorithm, which creates  $s$  inputs over the  $s$  slots, with one of them being the main one and is unmodified, while the others are randomly generated.

---

**Algorithm 2** Dummy Shuffling Refresh gadget

---

**Inputs:**

- $(x_1, \dots, x_\ell)$  s.t.  $\text{Decode}_f(x_1, \dots, x_\ell) = x$

- $s - 1$  fresh randomness

- the flags  $f$

**Output:**  $(\tilde{x}_1, \dots, \tilde{x}_\ell)$  s.t.  $\text{Decode}_f(\tilde{x}_1, \dots, \tilde{x}_\ell) = x$

- 1:  $S \leftarrow (0, \$, \dots, \$)$ , s.t.  $|S| = s$

- 2:  $S \leftarrow \text{Shuffle}_f(S)$

- 3:  $(\tilde{x}_1, \dots, \tilde{x}_\ell) \leftarrow (x_1 \oplus S_1, \dots, x_\ell \oplus S_\ell)$

- 4: **return**  $(\tilde{x}_1, \dots, \tilde{x}_\ell)$

---

2. **Evaluation:** The second phase evaluates every copy of the algorithm for its input. Only the algorithm located in the main slot performs the real computations. The refresh gadget after every AND gate takes its pre-shuffled randomness from the first phase and adds it to the gate's output.

3. **Output-selection:** This last phase concludes the implementation by getting every output of the  $s$  slots and applying the Unshuffle function with the flags to recover the output of the main slot. The other random outputs of the dummy slots are dismissed.

The authors prove that Dummy Shuffling with refreshes achieves algebraic security for the evaluation phase. Currently, Dummy Shuffling is the only solution proven algebraically resistant to any degree, simply by increasing the number of slots ( $s$  slots requires performing HDDA of degree  $d = s$  to break it), as the SEL masking scheme only has an algebraic proof up to the third degree.

Unlike the ISW masking scheme, instead of having  $\ell$  node vectors XORing to one of the selection vectors, in that case,  $s$  vectors equal to one of the selection vectors for an unknown subset of traces. However, this scheme alone is weak to correlation attacks, so the authors suggested that it should be combined with the ISW masking scheme, yet did not provide any details on how exactly it should be done and what security it would achieve.

**Conclusion** To summarize, Table 2 shows all the available countermeasures and best known attacks against them.

**Table 2:** Different available white-box countermeasures with their gate overhead for XOR and AND operations, given with the lowest time complexity white-box attack known to thwart it.  $\omega$  is the matrix multiplication exponent,  $|\mathcal{K}|$  is the number of selection vectors (4096 for the AES), and  $k_\tau$  is a small constant determined in function of the noise rate  $\tau$ .

| Scheme          | Reference | XOR cost   | AND cost               | Best attack       | Time $O(\cdot)$                                       |

|-----------------|-----------|------------|------------------------|-------------------|-------------------------------------------------------|

| ISW $_\ell$     | [ISW03]   | $\ell$     | $3\ell^2 - 2\ell$      | LDA               | $\mathcal{W}^\omega + \mathcal{W} \mathcal{K} $       |

| BU              | [BU18]    | 29         | 39                     | DCA $_{1/4}$      | $\mathcal{W}k_{1/4} \mathcal{K} $                     |

| DS $_s$         | [BU21]    | $s + 1$    | $6s + 2$               | DCA $_{(s-1)/2s}$ | $\mathcal{W}k_{(s-1)/2s} \mathcal{K} $                |

| SEL $_{\ell,2}$ | [SEL21]   | $\ell + 4$ | $2\ell^2 + 5\ell - 1$  | FLDA              | $\mathcal{W}^{\omega+1} +  \mathcal{K} \mathcal{W}^2$ |

| SEL $_{\ell,3}$ | [SEL21]   | $\ell + 9$ | $2\ell^2 + 15\ell - 2$ | FLDA              | $\mathcal{W}^{\omega+1} +  \mathcal{K} \mathcal{W}^2$ |

Since [CU24], at best, a countermeasure such as SEL $_{3,2}$  can force an attack to be in quartic complexity, which, in practice, results in very efficient attacks taking little time to recover the full key. To tackle this issue, we need a countermeasure with tunable parameters that can only be attacked in a time complexity exponential in these parameters.

## 4 Combining countermeasures

The idea suggested in [BU18, BU21, CU24] was to combine two countermeasures to prevent algebraic and correlation attacks. While it is clear that ISW is a good candidate for avoiding correlation attacks, there are two solutions to prevent algebraic attacks. The first is to use a nonlinear masking scheme based on high-degree monomials like BU or  $\text{SEL}_{1,d}$ , the second is Dummy Shuffling.

**Combining ISW with BU or SEL** We decided to not focus on the high-degree monomial-based masking schemes as none of them can achieve algebraic security of arbitrary order, as in [SEL21], the authors brought algebraic security up to degree three which is weak to HDDA of degree three (in time complexity  $O(\mathcal{W}^{3\omega-1} + |\mathcal{K}|\mathcal{W}^3)$ ). Furthermore, the noise rate of such schemes is lowering as the degree increases, which is a vulnerability that [CU23] highlighted. Therefore, we focused on combinations of ISW with Dummy Shuffling.

### 4.1 ISW then Dummy Shuffling

A first method to combine these two countermeasures would be to apply one on a circuit  $C' \leftarrow \text{ISW}(C)$ , then the second one  $C'' \leftarrow \text{DS}(C')$ . We will denote the transformation that applies ISW and then Dummy Shuffling to a circuit by  $\text{DS} \circ \text{ISW}$ . Analogously, we denote the transformation that applies Dummy Shuffling and then ISW to a circuit by  $\text{ISW} \circ \text{DS}$ . Interestingly, the order of application of the two countermeasures matters.

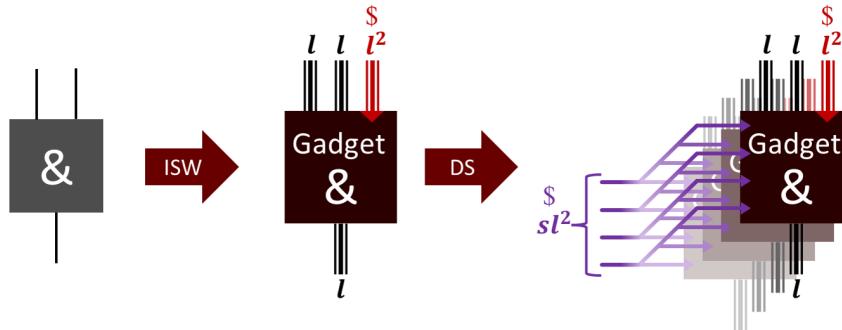

Applying the ISW masking scheme with  $\ell$  linear shares replaces in the original circuit  $C$  every bitwise gate by gadgets and every bit variable by  $\ell$  shares. Applying Dummy Shuffling with  $s$  slots to this modified circuit  $\text{ISW}(C)$  duplicates it  $s$  times, then generates the input-shuffling phase, the output-selection phase, and XORs pre-shuffled randomness to every AND gates constituting the ISW AND gadgets. The construction is illustrated in Figure 1.

**Figure 1:** Applying ISW and then Dummy Shuffling.

For such a scheme and given the flags  $f$ , a bit variable  $v$  will be shared of  $s\ell$  shares  $x_{i,j}, i \in (1, \dots, \ell), j \in (1, \dots, s)$ , such that:

$$\begin{aligned} v &= \text{Unshuffle}_f((x_{1,1} \oplus \dots \oplus x_{\ell,1}), \dots, (x_{1,s} \oplus \dots \oplus x_{\ell,s})) \\ &= \text{Unshuffle}_f(x_{1,1}, \dots, x_{1,s}) \oplus \dots \oplus \text{Unshuffle}_f(x_{\ell,1}, \dots, x_{\ell,s}) \end{aligned}$$

**Correlation analysis** In this case, determining the noise rate of the implementation would not give us information on how to perform the most efficient HODCA attack, as the noise rate would be computed using an algebraic function involving the  $s\ell$  shares, making the corresponding HODCA of order  $s\ell$ .

Instead, we propose an order- $\ell$  HODCA attack that consists of XORing the shares  $(x_{1,1} \oplus \dots \oplus x_{\ell,1})$ . This XOR result matches the decoding function when the main slot corresponds to the XORED shares which happens with probability  $\frac{1}{s}$ , but also when the main slot does not correspond but the random value that the XORing function takes is correct, which happens with probability  $\frac{s-1}{s} \cdot \frac{1}{2}$ . Therefore, the two function mismatches with probability  $p = \frac{s-1}{2s}$ , resulting to an HODCA attack of order  $\ell$  and noise  $p$ .

**Algebraic analysis** In [BU21], the authors showed that Dummy Shuffling resists HDDA of degree matching the number of dummy slots, here  $s - 1$ . Since ISW does not bring any algebraic resistance, HDDA of degree  $d = s$  can break  $DS \circ ISW$ , which has a time complexity of  $\mathcal{W}^{d\omega} + |\mathcal{K}|\mathcal{W}^d$ .

**Filtering analysis** It is possible to find a better complexity that solely depends on  $s$ , by performing a Higher-Order Filtering attack. Indeed, [CU24] proposed such an algorithm to filter multiple nodes simultaneously, allowing fixing any node vector to a desired value.

With  $DS \circ ISW$ , every XOR gates are refreshed using [Algorithm 2](#), which will XOR random values to the dummy slots, and a zero to the main slot. Even if the main slot is unknown, we know it is not located where these random values from refresh are equal to one. So, using Higher-Order filtering of order  $s - 1$ , we can choose the subset of traces where the node vectors corresponding to these shuffled random values equal one.

For this filtered subset of traces where this condition holds we can ensure that the last random value left free of constraints will always be equal to zero, hence fixing the main slot to a single slot. Now that the main slot is always the same, we removed the Dummy Shuffling algebraic security, making  $DS \circ ISW$  weak to an LDA attack. Performing  $HOF_{s-1}\text{-LDA}$  attack has a time complexity in  $\mathcal{W}^{s-1+\omega} + |\mathcal{K}|\mathcal{W}^{s-1}$ , which is better than HDDA of degree  $d = s$ .

## 4.2 Dummy Shuffling then ISW

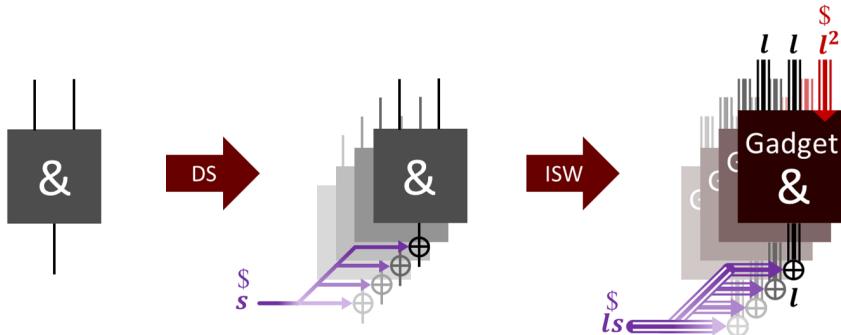

By applying Dummy Shuffling first, we duplicate the whole circuit  $C$  onto  $s$  slots, add the input-shuffling and the output-selection phases, and add pre-shuffled randomness to all the AND gates. Now, we apply ISW to this modified circuit  $DS(C)$  and replace every XOR and AND gates by XOR and AND gadgets, and every variable by  $\ell$  shares. Contrarily to  $DS \circ ISW$ , we can observe that the input-shuffling and output-selection phases are here protected by ISW, adding a new layer of obfuscation. The construction is illustrated in [Figure 2](#).

**Figure 2:** Applying Dummy Shuffling and then ISW.

**Security analysis** Since  $ISW \circ DS$  has the same decoding function as  $DS \circ ISW$ , we can also perform the same  $HODCA_{\ell,p}$  and  $HDDA_s$  attacks. However, here the pre-shuffled

randomness of Dummy Shuffling is shared, forcing the previous Higher Order Filtering LDA attack presented against  $DS \circ ISW$  to be of order  $\ell s - 1$ , and therefore to be impractical. Without this weakness,  $ISW_\ell \circ DS_s$  needs fewer slots  $s$  than  $DS_s \circ ISW_\ell$  to resist attack with time complexity as a function of  $s$ .

**Implementation size** Surprisingly, for the same parameters  $\ell$  and  $s$ ,  $ISW \circ DS$  has a different implementation size than  $ISW \circ DS$ , as shown experimentally in Table 3. Indeed, ISW and Dummy Shuffling have different costs of transforming an AND and a XOR gate. Since transforming an AND gate creates new XOR and AND gates, applying them in different order changes the overall size of the implementation.

**Table 3:** Comparison of the implementation size (in million of gates) between  $ISW_\ell \circ DS_s$  and  $DS_s \circ ISW_\ell$  applied to a 10-round AES (31k gates), using the implementation given in the `wboxkit` tool<sup>3</sup>.

|               |               | ISW $_\ell \circ DS_s$ |     |     |      |      |      | DS $_s \circ ISW_\ell$ |     |     |     |      |      |      |     |

|---------------|---------------|------------------------|-----|-----|------|------|------|------------------------|-----|-----|-----|------|------|------|-----|

|               |               | $s$                    | 2   | 3   | 4    | 5    | 6    | 7                      | $s$ | 2   | 3   | 4    | 5    | 6    | 7   |

| $l \setminus$ | $s \setminus$ | 2                      | 0.2 | 1.0 | 1.2  | 1.6  | 2.1  | 2.5                    | 2   | 0.4 | 1.0 | 1.3  | 1.8  | 2.2  | 2.7 |

| 2             | 2             | 0.2                    | 1.0 | 1.2 | 1.6  | 2.1  | 2.5  | 2                      | 0.4 | 1.0 | 1.3 | 1.8  | 2.2  | 2.7  |     |

| 3             | 3             | 0.7                    | 1.7 | 2.1 | 2.8  | 3.5  | 4.2  | 3                      | 0.9 | 1.7 | 2.1 | 2.9  | 3.7  | 4.5  |     |

| 4             | 4             | 1.1                    | 2.7 | 3.2 | 4.2  | 5.3  | 6.3  | 4                      | 1.3 | 2.4 | 3.1 | 4.3  | 5.6  | 6.8  |     |

| 5             | 5             | 1.6                    | 3.7 | 4.5 | 6.0  | 7.5  | 8.9  | 5                      | 1.9 | 3.3 | 4.2 | 6.0  | 7.7  | 9.5  |     |

| 6             | 6             | 2.1                    | 5.0 | 6.0 | 8.0  | 10.0 | 12.0 | 6                      | 2.5 | 4.3 | 5.5 | 7.9  | 10.3 | 12.7 |     |

| 7             | 7             | 2.7                    | 6.5 | 7.8 | 10.4 | 12.9 | 15.5 | 7                      | 3.2 | 5.4 | 7.0 | 10.1 | 13.2 | 16.3 |     |

**Theorem 1.** Let  $C$  be a circuit constituted of  $n_\oplus$  XOR gates and  $n_\wedge$  AND gates.

- $DS_s \circ ISW_\ell(C)$  has an overhead of  $(6s - 4)(\ell^2 - \ell)n_\wedge$  AND gates, and  $s(2\ell^2 - 2\ell)n_\wedge + \ell s n_\oplus$  XOR gates.

- $ISW_\ell \circ DS_s(C)$  has an overhead of  $(6s - 4)(\ell^2 - \ell)n_\wedge$  AND gates, and  $(6s - 4)(2\ell^2 - 2\ell)n_\wedge + \ell s n_\oplus$  XOR gates.

*Proof.*  $ISW_\ell$  transforms one AND gate into  $\ell^2 - \ell$  AND gates and  $2\ell^2 - 2\ell$  XOR gates, and transforms one XOR gate into  $\ell$  XOR gates. For the whole implementation (input-encoding, evaluation, and output-selection phases) Dummy Shuffling transforms one AND gate into  $6s - 4$  AND gates, and transforms one XOR gates into  $s$  XOR gates [BU21].

Let us begin by  $DS_s \circ ISW_\ell(C)$ : given a circuit  $C$  made of  $n_\wedge$  AND gates and  $n_\oplus$  XOR gates,  $ISW_\ell(C)$  will have  $(\ell^2 - \ell)n_\wedge$  AND gates and  $(2\ell^2 - 2\ell)n_\wedge + \ell n_\oplus$  XOR gates. Finally,  $DS_s \circ ISW_\ell(C)$  will have a total of  $(6s - 4)(\ell^2 - \ell)n_\wedge$  AND gates, and  $s((2\ell^2 - 2\ell)n_\wedge + \ell n_\oplus)$  XOR gates.

Likewise, for  $ISW_\ell \circ DS_s(C)$  and for the same circuit  $C$  with  $n_\wedge$  AND gates and  $n_\oplus$  XOR gates,  $DS_s(C)$  will have  $(6s - 4)n_\wedge$  AND gates and  $s n_\oplus$  XOR gates. Finally,  $ISW_\ell \circ DS_s(C)$  will have  $(6s - 4)(\ell^2 - \ell)n_\wedge$  AND gates and  $\ell s n_\oplus + (6s - 4)(2\ell^2 - 2\ell)n_\wedge$  XOR gates.  $\square$

In theory, both  $DS_s \circ ISW_\ell(C)$  and  $ISW_\ell \circ DS_s(C)$  have the same number of AND gates, but they have different numbers of XOR gates. More precisely,  $ISW \circ DS$  has  $(6 - \frac{4}{s})$  time more XOR gates. However, in practice,  $ISW \circ DS$  has less than  $DS \circ ISW$ . This can be explained by the pseudorandom generator used in `wboxkit` not being considered in the theoretical estimate.

**Conclusion** In general,  $ISW \circ DS$  has an equivalent implementation size as  $DS \circ ISW$  given the same parameter  $\ell$  and  $s$ , has the advantage of having obfuscated input-shuffling

<sup>3</sup>See <https://github.com/hellman/wboxkit>.

and output-selection phases, resists the same correlation and algebraic attacks, and has better resistance against filtering attacks. Therefore,  $\text{ISW} \circ \text{DS}$  should be preferred in any circumstances over  $\text{DS} \circ \text{ISW}$ .

## 5 Semi-Shuffled Secret Sharing Scheme: S5

Even if  $\text{ISW} \circ \text{DS}$  has tunable parameters on which its best-known attacks have exponential time complexity, its implementation size is heavy due to the successive application of countermeasures that have not been studied to be combined.

We propose S5, which, similarly to the SEL masking scheme [SEL21], proposes to replace a share of ISW with a nonlinear component, but here with Dummy Shuffling instead of a high-degree monomial. The design is unique as it merges a masking scheme that focuses on the gates with a countermeasure that acts on the whole implementation.

### 5.1 Definition of S5

**Decoding function** Instead of having copies of a whole implementation distributed over different slots like  $\text{ISW} \circ \text{DS}$ , we would like to have  $\ell$  shares as  $\text{ISW}_\ell$ , with the real value of the last share taken by one of the  $s$  *slotted shares* chosen randomly for each different input. We denote the  $S5$  masking schemes for  $\ell$  linear shares with one of them shuffled amongst  $s$  slots by  $S5_{\ell,s}$ .

Given the  $\ell + s - 1$  shares  $(x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s})$  of a bit variable  $x$ , the decoding function  $\text{DecodeDS}_f$  of Dummy Shuffling, and the flags  $f$ ,  $S5_{\ell,s}$  has the following decoding function:

$$\text{Decode}_f((x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s})) = x_1 \oplus \cdots \oplus x_{\ell-1} \oplus \text{DecodeDS}_f((x_{\ell,1}, \dots, x_{\ell,s}))$$

**Encoding function** As for  $\text{ISW}_\ell$ ,  $\ell - 1$  random values are required to encode a bit variable and fix the last share  $x_\ell$  being equal to the sum of these random values plus the original value. Then,  $s - 1$  supplementary random values are required for the dummy slots as in Dummy shuffling. The procedure is depicted in Algorithm 3.

---

**Algorithm 3** S5's Encoding function

---

**Input:**

- A bit variable  $z$  to share

- $\ell + s - 2$  fresh random values

- The flags  $f$

**Output:** The shares  $(z_1, \dots, z_\ell, z_{\ell,1}, \dots, z_{\ell,s})$ , such that

$$\text{Decode}_f((z_1, \dots, z_\ell, z_{\ell,1}, \dots, z_{\ell,s})) = z$$

- 1: **for**  $i \in (1 \cdots \ell - 1)$  **do**

- 2:      $z_i \leftarrow \$$

- 3: **end for**

- 4:  $z_{\ell,1} \leftarrow \bigoplus_{i=1}^{\ell-1} z_i$

- 5: **for**  $i \in (2 \cdots s)$  **do**

- 6:      $z_{\ell,i} \leftarrow \$$

- 7: **end for**

- 8:  $(z_{\ell,1} \cdots z_{\ell,s}) \leftarrow \text{Shuffle}_f((z_{\ell,1} \cdots z_{\ell,s}))$

- 9: **return**  $(z_1 \cdots z_{\ell-1}, z_{\ell,1} \cdots z_{\ell,s})$

---

**Xor gadget** Now that we can encode and decode our bit variables, we need to replace the bit gates with gadgets, such that they do not leak information while computing the

correct output. The XOR gadget is simple to perform, as for both the ISW masking scheme and Dummy Shuffling, this gadget only consists of XORing the shares individually.

Let  $(x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s})$  and  $(y_1 \cdots y_{\ell-1}, y_{\ell,1} \cdots y_{\ell,s})$  be the shares of two bit variables  $x$  and  $y$  of an  $S5_{\ell,s}$  such that

$$\begin{aligned}\text{Decode}_f((x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s})) &= x, \\ \text{Decode}_f((y_1 \cdots y_{\ell-1}, y_{\ell,1} \cdots y_{\ell,s})) &= y.\end{aligned}$$

We have:

$$\begin{aligned}\text{GadgetXOR}((x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s}), (y_1 \cdots y_{\ell-1}, y_{\ell,1} \cdots y_{\ell,s})) &= \\ ((x_1 \oplus y_1) \cdots (x_{\ell-1} \oplus y_{\ell-1}), (x_{\ell,1} \oplus y_{\ell,1}) \cdots (x_{\ell,s} \oplus y_{\ell,s}))\end{aligned}$$

**And gadget** We presented SecMult, the  $\text{ISW}_{\ell}$  AND gadget in [Algorithm 1](#), and explained its matrix representation.  $S5_{\ell,s}$  AND gadget for one slot ( $s = 1$ ) is exactly this same algorithm. For  $s > 1$ , to compute the values of all the slots, we will duplicate  $s$  time in the last row of the representation matrix.

Let  $(x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s})$  and  $(y_1 \cdots y_{\ell-1}, y_{\ell,1} \cdots y_{\ell,s})$  be the shares of two bit variables  $x$  and  $y$  of an  $S5_{\ell,s}$  such that

$$\begin{aligned}\text{Decode}_f((x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s})) &= x, \\ \text{Decode}_f((y_1 \cdots y_{\ell-1}, y_{\ell,1} \cdots y_{\ell,s})) &= y.\end{aligned}$$

$S5_{\ell,s}$  AND gadget has four steps:

- ▷ **Step 1:** As a regular  $\text{ISW}_{\ell-1}$  masking scheme, process the  $\ell - 1$  first shares with the ISW AND gadget by applying  $\text{SecMult}((x_1 \cdots x_{\ell-1}), (y_1 \cdots y_{\ell-1}))$ .

- ▷ **Step 2:** To compute the necessary values to determine the last  $\ell^{th}$  share of an  $\text{ISW}_{\ell}$  masking scheme, for each shuffled share  $i \in (1, \dots, s)$ , perform the last part of  $\text{SecMult}((x_1 \cdots x_{\ell-1}, x_{\ell,i}), (y_1 \cdots y_{\ell-1}, y_{\ell,i}))$  that corresponds to the last row of the matrix.

- ▷ **Step 3:** Recover the first  $(\ell - 1)$  shares by XORing every elements of the first  $(\ell - 1)$  line of the matrix.

- ▷ **Step 4:** Recover the last  $s$  shares by XORing every elements of the last  $s$  line of the matrix.

The AND gadget is depicted in [Algorithm 4](#), and also includes refresh functions to achieve security properties discussed in [Section 6](#).

**Example 5.** Consider the  $S5_{\ell=3,s=3}$  AND gadget, without the refresh functions: we receive  $(x_1, x_2, x_{3,1}, x_{3,2}, x_{3,3})$  and  $(y_1, y_2, y_{3,1}, y_{3,2}, y_{3,3})$ , the shares of two bit variables  $x$  and  $y$  such that  $\text{Decode}_f((x_1, x_2, x_{3,1}, x_{3,2}, x_{3,3})) = x$  and  $\text{Decode}_f((y_1, y_2, y_{3,1}, y_{3,2}, y_{3,3})) = y$ . We want to compute  $(z_1, z_2, z_{3,1}, z_{3,2}, z_{3,3})$  such that  $\text{Decode}_f((z_1, z_2, z_{3,1}, z_{3,2}, z_{3,3})) = z = x \cdot y$ .

Then, we can create a  $(\ell + s - 1) \times \ell$  matrix, here a  $5 \times 3$  matrix  $M$  filled with zeroes to represent the computations. Step 1 begins by computing the elements of the first  $\ell - 1 = 2$  columns and rows, that only depend on the linear part of the shares, namely  $x_1, x_2, y_1$ , and  $y_2$ . Then, Step 2 computes the rest of the operations that depend on the non-linear part:  $x_{3,1}, x_{3,2}, x_{3,3}, y_{3,1}, y_{3,2}$ , and  $y_{3,3}$ . Step 3 consists of XORing every element of the

---

**Algorithm 4** S5's AND gadget

---

**Inputs:**

- $(x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s})$  s.t.  $\text{Decode}_f((x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s})) = x$

- $(y_1 \cdots y_{\ell-1}, y_{\ell,1} \cdots y_{\ell,s})$  s.t.  $\text{Decode}_f((y_1 \cdots y_{\ell-1}, y_{\ell,1} \cdots y_{\ell,s})) = y$

- One shared pre-shuffled randomness (for  $\text{SPSR}_f$ )

- Two pre-shuffled randomness (for  $\text{Refresh}_f$ )

- $\frac{\ell(\ell-1)}{2}$  fresh randomness

**Output:**

- $(z_1 \cdots z_{\ell-1}, z_{\ell,1} \cdots z_{\ell,s})$  s.t.  $\text{Decode}_f((z_1 \cdots z_{\ell-1}, z_{\ell,1} \cdots z_{\ell,s})) = x \cdot y$

```

1:  $(x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s}) \leftarrow \text{Refresh}((x_1 \cdots x_{\ell-1}, x_{\ell,1} \cdots x_{\ell,s}))$

2:  $(y_1 \cdots y_{\ell-1}, y_{\ell,1} \cdots y_{\ell,s}) \leftarrow \text{Refresh}((y_1 \cdots y_{\ell-1}, y_{\ell,1} \cdots y_{\ell,s}))$

3:  $M \leftarrow (\ell + s - 1) \times \ell$  zero matrix

4: for  $i \in (1 \cdots \ell - 1)$  do ▷ Step 1: Handling linear shares

5:   for  $j \in (i + 1 \cdots \ell - 1)$  do

6:      $M_{i,j} \leftarrow \$$

7:      $M_{j,i} \leftarrow (M_{i,j} \oplus x_i \cdot y_j) \oplus x_j \cdot y_i$

8:   end for

9: end for

10: for  $i \in (1 \cdots \ell - 1)$  do

11:    $z_i \leftarrow x_i \cdot y_i$

12: end for

13: for  $i \in (1 \cdots \ell - 1)$  do ▷ Step 2: Handling shuffled shares

14:    $M_{i,\ell} \leftarrow \$$

15: end for

16: for  $k \in (1 \cdots s)$  do

17:   for  $i \in (1 \cdots \ell - 1)$  do

18:      $M_{k+\ell-1,i} \leftarrow (M_{i,\ell} \oplus x_i \cdot y_{\ell,k}) \oplus x_{\ell,k} \cdot y_i$

19:   end for

20: end for

21: for  $k \in (1 \cdots s)$  do

22:    $z_{\ell,k} \leftarrow x_{\ell,k} \cdot y_{\ell,k}$

23: end for

24: for  $i \in (1 \cdots \ell - 1)$  do ▷ Step 3: Computing the linear part of the result

25:   for  $j \in (1 \cdots \ell)$  do

26:     if  $i \neq j$  then

27:        $z_i \leftarrow z_i \oplus M_{i,j}$

28:     end if

29:   end for

30: end for

31:  $R \leftarrow \text{SPSR}_f$  ▷ Step 4: Computing the shuffled part of the result

32: for  $i \in (1 \cdots s)$  do

33:   for  $j \in (1 \cdots \ell - 1)$  do

34:      $z_{\ell,i} \leftarrow (z_{\ell,i} \oplus R_{i,j}) \oplus M_{i+\ell-1,j}$

35:   end for

36: end for

37: return  $(z_1 \cdots z_{\ell-1}, z_{\ell,1} \cdots z_{\ell,s})$

```

---

first  $\ell - 1 = 2$  lines to compute the linear part of  $z$ :  $z_1$  and  $z_2$ . Finally, the last Step 4 does the same for the last  $s = 3$  lines and computes  $z_{3,1}$ ,  $z_{3,2}$ , and  $z_{3,3}$ .

$$\begin{aligned} z_1 &\leftarrow x_1 \cdot y_1 & r_{1,2} & & r_{1,3} \\ z_2 &\leftarrow x_2 \cdot y_1 \oplus r_{1,2} \oplus x_1 \cdot y_2 & x_2 \cdot y_2 & & r_{2,3} \\ z_{3,1} &\leftarrow x_1 \cdot y_{3,1} \oplus r_{1,3} \oplus x_{3,1} \cdot y_1 & x_2 \cdot y_{3,1} \oplus r_{2,3} \oplus x_{3,1} \cdot y_2 & x_{3,1} \cdot y_{3,1} \\ z_{3,2} &\leftarrow x_1 \cdot y_{3,2} \oplus r_{1,3} \oplus x_{3,2} \cdot y_1 & x_2 \cdot y_{3,2} \oplus r_{2,3} \oplus x_{3,2} \cdot y_2 & x_{3,2} \cdot y_{3,2} \\ z_{3,3} &\leftarrow x_1 \cdot y_{3,3} \oplus r_{1,3} \oplus x_{3,3} \cdot y_1 & x_2 \cdot y_{3,3} \oplus r_{2,3} \oplus x_{3,3} \cdot y_2 & x_{3,3} \cdot y_{3,3} \end{aligned}$$

One can observe that the different slots do not interact with each other, meaning that, given  $i, j \in \{1, 2, 3\}$ ,  $i \neq j$ ,  $x_{3,i}$ ,  $y_{3,i}$  and  $z_{3,i}$  does not interact with  $x_{3,j}$ ,  $y_{3,j}$  and  $z_{3,j}$ . Therefore, given flags  $f$  and a corresponding main slot  $m \in \{1, 2, 3\}$ ,  $\text{DecodeDS}_f(z_{3,1}, z_{3,2}, z_{3,3}) = z_{3,m}$  only depends on  $x_{3,m}$  and  $y_{3,m}$ . Therefore:

$$\begin{aligned} z &= z_1 \oplus z_2 \oplus \text{DecodeDS}_f(z_{3,1}, z_{3,2}, z_{3,3}) \\ &= z_1 \oplus z_2 \oplus z_{3,m} \\ &= \text{SecMult}((x_1, x_2, x_{3,m})), ((y_1, y_2, y_{3,m})) \\ &= (x_1 \oplus x_2 \oplus x_{3,m}) \cdot (y_1 \oplus y_2 \oplus y_{3,m}) \\ &= (x_1 \oplus x_2 \oplus \text{DecodeDS}_f(x_{3,1}, x_{3,2}, x_{3,3})) \cdot (y_1 \oplus y_2 \oplus \text{DecodeDS}_f(y_{3,1}, y_{3,2}, y_{3,3})) \\ &= x \cdot y \end{aligned}$$

**Randomness** As explained in the following [Section 6](#), to achieve SNI and algebraic security, S5 need to be refreshed. A refresh function takes for input the shares of a variable and adds randomness to every share without modifying its decoding value. S5 uses three type of randomness:

- *Fresh randomness*: The usual randomness produced by a pseudo-random number generator in the white-box setting. Used to generate the two other types of randomness, to encode the input values of a circuit, and in the AND gadget. A bit variable  $v$  receiving fresh randomness is denoted by  $v \leftarrow \$$ .

- *Pre-shuffled randomness*: This randomness is constituted of  $s$  bit values, that, once XORed to a bit variable over  $s$  slots, ensures that the main slot remains unmodified.

- *Shared pre-shuffled randomness*: Lastly, it is possible to share pre-shuffled randomness over  $\ell - 1$  shares. We end up with a  $s \times (\ell - 1)$  matrix  $R$ , such that the XOR of each of its lines is equal to one of the  $s$  bits of the pre-shuffled randomness.

**Pre-shuffled randomness** In [Section 6](#), we show that the shuffled part of the two inputs of S5 AND gadget should be refreshed to achieve algebraic security, which can be done using the dummy shuffling refresh function. Generating a pre-shuffled randomness over  $s$  slots requires  $s - 1$  fresh randomness, without counting the number of randomness involved in the Decode and Shuffle function of Dummy Shuffling. Applying the shuffle function with the flags  $f$  onto a zero followed by the random values creates pre-shuffled randomness, which, once XORed with a bit variable over multiple slots, ensures that the main slot is not modified. Refreshing the shuffled part of S5 is depicted in [Algorithm 5](#):

**Shared pre-shuffled randomness** In the  $S5_{\ell,s}$  AND gadget, we create a  $(\ell + s - 1) \times \ell$  matrix  $M$ , which has its last  $s$  rows filled with computations necessary to create the  $s$  shuffled shares of the output. Let us denote the  $s \times (\ell - 1)$  matrix containing these last rows by  $S$ . In [Section 6](#), we show that to achieve SNI security of the XOR gadget, we need to refresh every value of the  $S$  matrix. Let us denote the refreshed matrix by  $\tilde{S}$ .

---

**Algorithm 5** S5's shuffled refresh gadget

---

**Inputs:**

- $(x_1, \dots, x_{\ell-1}, x_{\ell,1}, \dots, x_{\ell,s})$  s.t.  $\text{Decode}_f((x_1, \dots, x_{\ell-1}, x_{\ell,1}, \dots, x_{\ell,s})) = x$

- $s - 1$  fresh randomness

- the flags  $f$

**Output:**  $(x_1, \dots, x_{\ell-1}, \tilde{x}_{\ell,1}, \dots, \tilde{x}_{\ell,s})$  s.t.  $\text{Decode}_f((x_1, \dots, x_{\ell-1}, \tilde{x}_{\ell,1}, \dots, \tilde{x}_{\ell,s})) = x$

- 1:  $S \leftarrow (0, \$, \dots, \$)$ , s.t.  $|S| = s$

- 2:  $S \leftarrow \text{Shuffle}_f(S)$

- 3:  $\{x_1 \dots x_{\ell-1}, \tilde{x}_{\ell,1} \dots \tilde{x}_{\ell,s}\} \leftarrow \{x_1 \dots x_{\ell-1}, x_{\ell,1} \oplus S_1, \dots, x_{\ell,s} \oplus S_s\}$

- 4: **return**  $(x_1, \dots, x_{\ell-1}, \tilde{x}_{\ell,1}, \dots, \tilde{x}_{\ell,s})$

---

The first constraint to such refresh function is that given the main slot  $m \in (1, \dots, s)$ , we need to ensure that  $\bigoplus_{i=0}^{\ell-1} S_{m,i} = \bigoplus_{i=0}^{\ell-1} \tilde{S}_{m,i}$ , but we don't know the main slot without the shuffle or unshuffle functions, which we cannot use in the gadget as it would leak information on the flag. The second constraint is that the shuffled shares should not interact with each other.

A first idea would be to apply the refresh function of [Algorithm 2](#) to each column of  $S$ . This would ensure SNI property and the previously exposed constraints, but performing  $\ell - 1$  Shuffle call would be too heavy. Instead, shuffle one randomness gives a  $s$ -length vector  $r$  such that  $r_m = 0$ , which we can transform in a  $(\ell + s - 1) \times \ell$  matrix  $R$  by sharing each of its  $s$  values over  $\ell - 1$  shares. XORing  $S$  and  $R$  gives a refreshed matrix that respects the two constraints, and, as detailed in [Section 6](#), ensures SNI security. The creation of this matrix denoted by *Shared pre-shuffled randomness* is given in [Algorithm 6](#)

---

**Algorithm 6** S5's Shared pre-shuffled randomness (SPSR)

---

**Inputs:**

- $s - 1 + \frac{\ell(\ell-1)}{2}$  fresh randomness

- the flags  $f$

**Output:** A two dimensional array  $R$  containing  $s$  vectors of  $x$  elements such that

$$\text{Decode}_f((R_{1,1} \oplus \dots \oplus R_{1,x}), \dots, (R_{s,1} \oplus \dots \oplus R_{s,x})) = 0$$

- 1:  $S \leftarrow (0, \$, \dots, \$)$ , s.t.  $|S| = s$

- 2:  $S \leftarrow \text{Shuffle}_f(S)$

- 3: **for**  $k \in (1, \dots, \ell - 1)$  **do**

- 4:      $R_i \leftarrow (S_i, 0, \dots, 0)$ , s.t.  $|R_i| = \ell - 1$

- 5:     **for**  $i \in (1, \dots, s)$  **do** ▷ SNI refresh gadget 4b of [BBD<sup>+</sup>16]

- 6:         **for**  $j \in (i + 1, \dots, s)$  **do**

- 7:              $r \leftarrow \$$

- 8:              $R_{k,i} \leftarrow S_i \oplus r$

- 9:              $R_{k,j} \leftarrow S_j \oplus r$

- 10:         **end for**

- 11:     **end for**

- 12: **end for**

- 13: **return**  $R$

---

**Phases** On the whole, S5 uses shuffle functions from Dummy Shuffling and therefore needs the three-phased structure depicted in [Definition 4](#). The only difference is the addition of the shared pre-shuffled randomness, which needs to be pre-computed and shared in the first input-encoding phase.

## 5.2 S5 analysis

**Higher-order attack analysis** Firstly, we show in Section 6 that  $S5_{\ell,s}$  has the same algebraic resistance against algebraic attacks as dummy shuffling with  $s$  slots, and therefore is only broken by HDDA of degree  $d \geq s$ . By design,  $S5_{\ell,s}, \ell > 1$  resists the DCA attack, as the linear shares do not carry full information on the variable being shared. However, given  $\tau$ , the noise rate of  $S5_{\ell,s}$ ,  $HODCA_{\mathcal{O},\tau}$  of order  $\mathcal{O} = \ell$  can break it.

**Proposition 1.** *The noise rate of  $S5_{\ell,s}$  is  $\tau = \frac{s-1}{2s}$ .*

*Proof.* Let a variable  $x$  being encoded to the shares  $(x_1, \dots, x_{\ell-1}, x_{\ell,1}, \dots, x_{\ell,s})$  by  $S5_{\ell,s}$  with the flags  $f$ . By definition, we have:

$$\begin{aligned} x &= \text{Decode}_f((x_1 \dots x_{\ell-1}, x_{\ell,1} \dots x_{\ell,s})) \\ &= x_1 \oplus \dots \oplus x_{\ell-1} \oplus \text{DecodeDS}_f(x_{\ell,1}, \dots, x_{\ell,s})) \end{aligned}$$

Choosing the linear function  $f(x_1, \dots, x_{\ell-1}, x_{\ell,1}) = x_1 \oplus \dots \oplus x_{\ell-1} \oplus x_{\ell,1}$  will match the decoding function's output depending on  $x_{\ell,1}$ : when  $x_{\ell,1}$  represents the main slot, the linear function is perfectly matching the decoding function, when  $x_{\ell,1}$  is a dummy slot, the linear function will match the decoding function with one-half probability. Therefore, since  $x_{\ell,1}$  is a dummy slot with probability  $\frac{s-1}{s}$ , the linear and decoding functions will have different outputs with probability  $\frac{s-1}{2s} = \tau$ .  $\square$

**Filtering analysis** Let a variable  $x$  being encoded by  $S5_{\ell,s}$  with the flags  $f$  to the shares  $(x_1, \dots, x_{\ell-1}, x_{\ell,1}, \dots, x_{\ell,s})$ . Using a higher-order filtering attack, one can fix the  $s$  shuffled shares  $(x_{\ell,1}, \dots, x_{\ell,s})$  to zero (or one) to ensure that, no matter where the main slot is located, its corresponding shuffled share would remain constant for all the subset of traces for whose this condition holds, making the scheme vulnerable to an LDA attack. So,  $HOF_s$ -LDA breaks  $S5_{\ell,s}$  and has a time complexity in  $O(\mathcal{W}^{\omega+s} + |\mathcal{K}|\mathcal{W}^{s+1})$ , which is better than  $HDDA_d$ .

**Implementation cost** Let  $C$  be a circuit to protect with  $S5_{\ell,s}$ , and let  $n_{\oplus}$  and  $n_{\wedge}$  be its number of XOR and AND gates, respectively. As for Dummy Shuffling, the implementation is constituted of three phases. To estimate the implementation cost, we need to estimate the cost of each phase. For the first phase, we need to estimate the cost of the two pre-shuffled randomness and the shared pre-shuffled randomness used at each AND gate of  $C$ . However, since the number of inputs is negligible compared to  $n_{\wedge}$ , we do not need to estimate the cost of encoding the input.

We need to generate three pre-shuffled randomness with one used to generate a shared pre-shuffled randomness per AND gate in the original circuit  $C$ . In [BU21], the authors estimated the cost of performing an input shuffling to  $4s \cdot n_{\wedge}$ . Since we need three per AND gate, we end up with a cost of  $12s \cdot n_{\wedge}$  to generate the pre-shuffled randomness.

One of these three pre-shuffled randomness needs to be shared, which is equivalent to estimate the cost of Algorithm 6, which performs  $\ell - 1$  times two XOR over  $\sum_{i=1}^{s-1} i = \frac{\ell(\ell-1)}{2}$  combinations, for a total of  $(\ell - 1)s(s - 1)$  operations. In total, the number of gates  $G_{IE}$  of the first input-encoding phase is  $G_{IE} = (\ell - 1)s(s + 11)$ .

For the second phase, we need to estimate the cost of the gadgets. The XOR gadget performs a XOR per couple of input shares, so costs  $(\ell + s - 1)n_{\oplus}$  operations. The four steps of  $S5_{\ell,s}$  AND gadget has different costs:  $2\ell(\ell - 1) + \ell - 1 = \text{step}_1$ ,  $4s(\ell - 1) + s = \text{step}_2$ ,  $\ell(\ell - 1) = \text{step}_3$ , and  $2s(\ell - 1) = \text{step}_4$ . In total, the second phase costs:

$$\begin{aligned} G_E &= (\text{step}_1 + \text{step}_2 + \text{step}_3 + \text{step}_4)n_{\wedge} + (\ell + s - 1)n_{\oplus} \\ &= ((\ell - 1)(3\ell + 6s) + \ell + s - 1)n_{\wedge} + (\ell + s - 1)n_{\oplus} \end{aligned}$$

Lastly, the output decoding phase applies the decoding function to every output, but since the number of outputs is negligible compared to the number of gates  $n_{\oplus}$  and  $n_{\wedge}$ , we conclude that the total cost of the implementation to transform a circuit  $C$  to  $S5_{\ell,s}(C)$  is:

$$G_{IS} + G_E = ((\ell - 1)(s(s + 11) + 3\ell + 6s) + \ell + s - 1)n_{\wedge} + (\ell + s - 1)n_{\oplus}$$

### 5.3 S5 and ISW $\circ$ DS comparison

**Theoretic implementation cost** Let  $C$  be a circuit with  $n_{\oplus}$  and  $n_{\wedge}$  number of XOR and AND gates, respectively. We showed in [Theorem 1](#) that the total implementation size for  $ISW_{\ell}\circ DS_s(C)$  (the more secure order of application of the two countermeasures) has a total implementation size in  $(6s - 4)(3\ell^2 - 3\ell)n_{\wedge} + \ell s n_{\oplus}$  gates, compared to  $((\ell - 1)(s(s + 11) + 3\ell + 6s) + \ell + s - 1)n_{\wedge} + (\ell + s - 1)n_{\oplus}$  for  $S5_{\ell,s}(C)$ .

We can observe that to transform a AND gate,  $S5_{\ell,s}(C)$  scales quadratically with both  $\ell$  and  $s$ , while  $ISW_{\ell}\circ DS_s(C)$  scales quadratically with  $\ell$  but only linearly with  $s$ . Moreover, the AND gate transformation of  $ISW_{\ell}\circ DS_s(C)$  is less expensive when  $\ell = s$  than  $S5_{\ell,s}(C)$ . However, even if the XOR gate transformation scale linearly for both  $s$  and  $\ell$  for both  $S5_{\ell,s}(C)$  and  $ISW_{\ell}\circ DS_s(C)$ , when  $\ell = s$ , it scales linearly with  $S5_{\ell,s}(C)$  and quadratically with  $ISW_{\ell}\circ DS_s(C)$ .

**In-practice implementation cost** [Table 4](#) shows the implementation size differences for a 10-round AES. S5 has a lower Implementation size for similar parameters, with a proportional difference increasing with  $\ell$  and  $s$ . This huge difference can be explained for two main reasons: the first is that there are more XOR gates than AND gates in the AES base implementation (62% XOR, 20% AND, 18% NOT).

The second is that for ISW and for Dummy Shuffling, the `wboxkit` tool creates a pseudo-random number generator (PRNG) to generate fresh randomness. In a circuit transformed by Dummy Shuffling, a first PRNG is created, and then, by applying ISW, it is encoded and a second one is created, which is much more heavy, while not accounted for in the theory. Whereas for S5, only one PRNG is created.

**Table 4:** Comparison of the implementation size (in million of gates) between  $ISW_{\ell}\circ DS_s$  and  $S5_{\ell,s}$  applied to a 10-round AES (31k gates), using the implementation given in the `wboxkit` tool (<https://github.com/hellman/wboxkit>), and our S5 implementation (<https://github.com/S5white-box/code>).

|     |     | ISW $\circ$ DS $_s$ |     |     |      |      |      | S5 $_{\ell,s}$ |     |     |     |     |     |     |     |

|-----|-----|---------------------|-----|-----|------|------|------|----------------|-----|-----|-----|-----|-----|-----|-----|

|     |     | $s$                 | 2   | 3   | 4    | 5    | 6    | 7              | $s$ | 2   | 3   | 4   | 5   | 6   | 7   |

| $l$ | $l$ | 2                   | 0.2 | 1.0 | 1.2  | 1.6  | 2.1  | 2.5            | 3   | 0.0 | 0.4 | 0.5 | 0.6 | 0.8 | 0.9 |

| 2   | 2   | 0.7                 | 1.7 | 2.1 | 2.8  | 3.5  | 4.2  | 5              | 0.3 | 0.6 | 0.7 | 0.9 | 1.1 | 1.3 |     |

| 3   | 3   | 1.1                 | 2.7 | 3.2 | 4.2  | 5.3  | 6.3  | 7              | 0.6 | 0.9 | 1.0 | 1.3 | 1.5 | 1.7 |     |

| 4   | 4   | 1.6                 | 3.7 | 4.5 | 6.0  | 7.5  | 8.9  | 8              | 0.8 | 1.2 | 1.4 | 1.7 | 2.0 | 2.3 |     |

| 5   | 5   | 2.1                 | 5.0 | 6.0 | 8.0  | 10.0 | 12.0 | 9              | 1.2 | 1.6 | 1.9 | 2.3 | 2.6 | 3.0 |     |

| 6   | 6   | 2.7                 | 6.5 | 7.8 | 10.4 | 12.9 | 15.5 | 10             | 1.6 | 2.1 | 2.5 | 2.9 | 3.4 | 3.9 |     |

| 7   | 7   |                     |     |     |      |      |      |                |     |     |     |     |     |     |     |

**Conclusion** Both  $ISW_{\ell}\circ DS_s$  and  $S5_{\ell,s}$  are efficient countermeasures against state-of-the-art attacks, and have different characteristics so should both be considered as valuable options against gray-box attacks in the white-box context, however, S5 shows being more efficient in practice.

We also recall that [\[BU21\]](#) described a bit-sliced implementation of dummy shuffling by filling a 64-bit CPU register with one variable from 64 slots. Contrarily to  $ISW_{\ell}\circ DS_s$ ,  $S5_{\ell,s}$  can not benefit from this technique due to interactions of unslotted and slotted variables.

Lastly, even if S5 is more efficient in practice, we recommend both countermeasures as they might not have the same weaknesses for future attacks, as we showed that slight differences in the structure are enough to create a vulnerability (see [Section 4](#)).

## 6 Security analysis

In this section, we discuss and prove the security of the three combined schemes against the relevant trace-based gray-box attacks, mainly correlation (HODCA) and algebraic (HDDA).

**Algebraic security** First, we reproduce the relevant definitions and results about the dummy shuffling from [\[BU21\]](#). The *error* of a Boolean function  $f : \mathbb{F}_2^n \rightarrow \mathbb{F}_2$  is given by  $\text{err}(f) = \min(|f|, |f \oplus 1|)/2^n$ .

**Definition 5.** For an implementation  $C : \mathbb{F}_2^n \rightarrow \mathbb{F}_2^m$ , the set  $\mathcal{F}^{(d)}(C)$  denotes all functions obtained by combining intermediate functions computed in  $C$  with a function of degree at most  $d$ . Elements of this set are Boolean functions  $f$  mapping  $\mathbb{F}_2^n$  to  $\mathbb{F}_2$ .

**Definition 6** (Scheme [\[BU21\]](#)). Let  $F : \mathbb{F}_2^n \rightarrow \mathbb{F}_2^m$  be a function. A *scheme  $S$  computing  $F$*  consists of

1. an *encoding function*  $S.\text{enc}(x, r_e) : \mathbb{F}_2^n \times \mathbb{F}_2^{|r_e|} \rightarrow \mathbb{F}_2^{n'}$ ;

2. an *implementation*  $S.\text{comp}(x', r_c) : \mathbb{F}_2^{n'} \times \mathbb{F}_2^{|r_c|} \rightarrow \mathbb{F}_2^{m'}$ ;

3. a *decoding function*  $S.\text{dec}(y') : \mathbb{F}_2^{m'} \rightarrow \mathbb{F}_2^m$ .

**Definition 7** ( $\tau$ -error- $d$ -AS scheme [\[BU21\]](#)). Let  $S$  be a scheme and let  $d \geq 1$  be an integer. Let  $\tau$  be the minimum error among all non-trivial functions from  $\mathcal{F}^{(d)}(S.\text{comp})$  composed with  $S.\text{enc} = S.\text{enc}(x, r_e)$  for any *fixed*  $x = \tilde{x} \in \mathbb{F}_2^n$ :

$$\tau = \min \left\{ \text{err} ( f(S.\text{enc}(\tilde{x}, \cdot), \cdot) ) \mid f(x, r_c) \in \mathcal{F}^{(d)}(S.\text{comp}) \setminus \{\mathbf{0}, \mathbf{1}\}, \tilde{x} \in \mathbb{F}_2^n \right\},$$

where the error is computed over  $r_e, r_c$ . If  $\tau > 0$ , the scheme  $S$  is said to be *degree- $d$  algebraically secure with error  $\tau$  ( $\tau$ -error- $d$ -AS)*.

### 6.1 Definitions of schemes

First, we recall the basic dummy shuffling scheme (called “the evaluation-phase model”, EPM) from [\[BU21\]](#).

**Definition 8** (Scheme  $S_s^{DS}$ ). Let  $C : \mathbb{F}_2^n \rightarrow \mathbb{F}_2^m$  be an implementation and let  $s \geq 2$ . Define the scheme  $S_s^{DS}(C)$  with the following phases:

- $S5_{\ell,s}.\text{enc}(x, r_e) : \mathbb{F}_2^n \times \mathbb{F}_2^{|r_e|} \rightarrow \mathbb{F}_2^{\tilde{n}}$  creates extra  $s - 1$  fully random inputs, derives random shuffling flags  $f$  from the input randomness  $r_e$ , and shuffles all the inputs using these flags (*c.f.* [Subsection 3.4](#)). Note  $\tilde{n} = n \times s$ .

- $S5_{\ell,s}.\text{comp}(x) : \mathbb{F}_2^{\tilde{n}} \rightarrow \mathbb{F}_2^{\tilde{m}}$  evaluates  $C$  at each of the  $s$  shuffled inputs (independently) and outputs all the  $s$  outputs. Here  $\tilde{m} = m \times s$ .

- $S5_{\ell,s}.\text{dec}(x, f) : \mathbb{F}_2^{\tilde{n}} \times \mathbb{F}_2^{|f|} \rightarrow \mathbb{F}_2^m$  unshuffles the  $s$  outputs from the previous phase using the flags  $f$  (which need to be securely passed from the encoding phase) and outputs the right output. This phase is only defined for the correctness and is not covered by security analysis in [\[BU21\]](#).

Before applying dummy shuffling, the circuit needs to be “refreshed”.

**Definition 9** (Refreshed Circuit). Let  $C(x) : \mathbb{F}_2^n \rightarrow \mathbb{F}_2^m$  be a Boolean circuit implementation with at most  $n_a$  AND gates. Define the *refreshed circuit*  $\tilde{C}(x, r) : \mathbb{F}_2^n \times \mathbb{F}_2^{n_a} \rightarrow \mathbb{F}_2^m$  as follows. Replace each AND gate  $a_k = z_i \wedge z_j$  in  $C$ ,  $1 \leq k \leq n_a$  by the circuit  $a'_k = r_k \oplus a_k = r_k \oplus (z_i \wedge z_j)$ , where  $r_k$  is the  $k$ -th extra bit; each wire using  $a_k$  is rewired to use  $a'_k$ .

In our security proofs, we reduce the new combined schemes to the original dummy shuffling scheme  $S_s^{DS}$ , and then apply the main theorem from [BU21].

**Theorem 2** ([BU21]). *Let  $C$  be an implementation and  $s \geq 2$  an integer. The dummy shuffling scheme  $S = S_s^{DS}(\tilde{C})$  is  $\tau$ -error- $d$ -AS for any  $1 \leq d \leq s-1$ , with  $\tau \geq 2^{-2d} \cdot (s-d)/s$ .*

We now formally define the three schemes of countermeasure combinations considered in the paper. The main purpose of this is specifying the part of the implementation covered by the proof: the operations’ gadgets excluding any shuffling/sharing or decoding operations (in line with existing state-of-the-art of dummy shuffling / ISW). For brevity, we will only describe the main phase (`comp`) of each scheme.

**Definition 10** (Scheme  $S5_{\ell,s}$ ). Let  $C : \mathbb{F}_2^n \rightarrow \mathbb{F}_2^m$  be an implementation and let  $l \geq 2, s \geq 2$ . Define the scheme  $S5_{\ell,s}(C)$  with  $S5_{\ell,s}.\text{comp}(x, r_c) : \mathbb{F}_2^{\tilde{n}} \times \mathbb{F}_2^{|r_c|} \rightarrow \mathbb{F}_2^{\tilde{m}}$  as follows. The input  $x$  consists of  $n$  lists of  $s + \ell - 1$  share each, as well as  $3n_a$  groups of preshuffled shared randomness ( $\ell$  bits each). The computation proceeds by applying the  $S5_{\ell,s}$  gadgets according to the circuit  $C$ , using fresh randomness from  $r_c$  and the preshared randomness from  $x$ .

*Remark 1.* The S5’s AND gadget already includes an equivalent of the refreshing, therefore  $S5_{\ell,s}$  is intended to be applied directly to the original circuit  $C$ , without the refreshing circuit transformation.

**Definition 11** (Scheme  $S_{\ell,s}^{DS \circ ISW}$ ). Let  $C : \mathbb{F}_2^n \rightarrow \mathbb{F}_2^m$  be an implementation and let  $l \geq 2, s \geq 2$ . Let  $C_{ISW}(x, r'_c)$  denote the circuit where the gates of  $C$  are replaced by the ISW gadgets and  $r'_c$  denotes the extra randomness used by these gadgets. Observe that  $C_{ISW}$  has  $n_a \ell^2$  AND gates, where  $C$  has  $n_a$  AND gates. Define the scheme  $S_{\ell,s}^{DS \circ ISW}(C)$  with  $S_{\ell,s}^{DS \circ ISW}.\text{comp}(x, r_c) : \mathbb{F}_2^{s\ell n + sn_a \ell^2} \times \mathbb{F}_2^{|r_c|} \rightarrow \mathbb{F}_2^{\ell sm}$  in the same way as  $S_s^{DS}(\tilde{C}_{ISW}).\text{comp}$ , where an extra randomness  $r'_c$  used by  $C_{ISW}$  is included (in  $s$  copies) in  $r_c$ . Observe that  $\tilde{C}_{ISW}$  has input size extended from  $\ell n$  to  $\ell n + n_a \ell^2$  due to the refresh bits.