PhD-FSTM-2022-143 The Faculty of Science, Technology and Medicine

## DISSERTATION

Defence held on 22/11/2022 in Esch-Sur-Alzette

to obtain the degree of

# DOCTEUR DE L'UNIVERSITÉ DU LUXEMBOURG

### **EN INFORMATIQUE**

by

# Lorenzo SPIGNOLI

Born on 11 July 1990 in Rome, (Italy)

## SIDE-CHANNEL COUNTERMEASURES IN THE PROBING MODEL

## Dissertation defence committee

Dr Jean-Sébastien Coron, dissertation supervisor Professor, Université du Luxembourg

Dr Ingrid Verbauwhede Professor, Katholieke Universiteit Leuven

Dr Alex Biryukov, Chairman Professor, Université du Luxembourg

Dr Francois-Xavier Standaert Professor, Université Catholique de Louvain

Dr David Naccache, Vice Chairman Professor, Ecole Normale Supérieure

A chi non ha mai vinto. A chi non è mai vinto.

## Contents

| 1        | Inti           | roduct | ion                                                           | 3  |

|----------|----------------|--------|---------------------------------------------------------------|----|

|          | 1.1            | Histor | rical vs Modern Cryptography                                  | 3  |

|          | 1.2            | Symm   | netric vs Asymmetric Cryptography                             | 5  |

|          | 1.3            | Black- | Box Model vs Physical Cryptanalysis                           | 7  |

|          |                | 1.3.1  | Side-Channel Analysis                                         | 8  |

| <b>2</b> | Pre            | limina | ries                                                          | 11 |

|          | 2.1            | Circui | its                                                           | 11 |

|          | 2.2            | Maski  | ng Countermeasure                                             | 12 |

|          | 2.3            | Advar  | nced Encryption Standard                                      | 13 |

|          |                | 2.3.1  | Specifications of Rijndael                                    | 13 |

| 3        | $\mathbf{Sid}$ |        | nnel Analysis                                                 | 19 |

|          | 3.1            | The IS | SW Model                                                      | 19 |

|          |                | 3.1.1  | Perfect Privacy for Stateless Circuits                        | 20 |

|          |                | 3.1.2  | Perfect Privacy for Stateful Circuits                         | 23 |

|          |                | 3.1.3  | Random Probing Model                                          | 25 |

|          |                | 3.1.4  | Statistical Privacy for Stateless Circuits                    | 27 |

|          |                | 3.1.5  | Statistical Privacy for Stateful Circuits                     | 30 |

|          | 3.2            | Rivair | n-Prouff Masking                                              | 31 |

|          |                | 3.2.1  | Masking of the S-box                                          | 32 |

|          |                | 3.2.2  | Masking the whole AES                                         | 35 |

|          | 3.3            | Strong | g Non-Interference                                            | 38 |

|          |                | 3.3.1  | NI and SNI definitions                                        | 38 |

|          |                | 3.3.2  | SNI Gadgets                                                   | 39 |

|          | 3.4            | Regio  | n Probing Model                                               | 43 |

|          |                | 3.4.1  | Leakage Rate and Regional Probing Model                       | 43 |

|          |                | 3.4.2  | About [ISW03], Regional Privacy and Re-Randomization Property | 44 |

|               |       | 3.4.3   | Privacy in the Stateless Regional Probing Model          | 45 |

|---------------|-------|---------|----------------------------------------------------------|----|

|               |       | 3.4.4   | Privacy in the Stateful Regional Probing Model           | 49 |

|               | 3.5   | Softwa  | are Probing Model                                        | 51 |

| 4             | Sec   | ure W   | ire Shuffling in the Probing Model                       | 53 |

|               | 4.1   | Rando   | om Gate-Probing Model                                    | 55 |

|               | 4.2   | Shuff   | ing Countermeasure in Stateless Setting                  | 56 |

|               |       | 4.2.1   | Description                                              | 57 |

|               |       | 4.2.2   | Shuffling Security and Composition                       |    |

|               |       | 4.2.3   | Improved Time-Complexity                                 |    |

|               |       | 4.2.4   | Shuffling for Pure Circuit Model                         |    |

|               | 4.3   | Shuff   | ing Countermeasure in Stateful Setting                   | 65 |

|               |       | 4.3.1   | Iterated Cyclic Shifts                                   | 66 |

|               |       | 4.3.2   | Randomizing Network                                      | 67 |

|               |       | 4.3.3   | Composition in the statistical stateful model            | 69 |

|               | 4.4   | Imple   | mentation                                                | 70 |

| 5             | Riv   | ain-Pr  | ouff on Steroids: Faster and Stronger Masking of the AES | 73 |

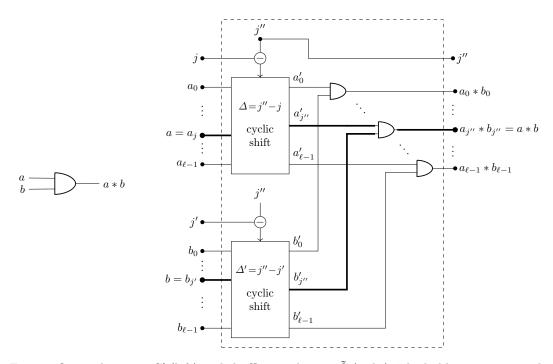

| 0             | 5.1   |         | Based Multiplication                                     |    |

|               | 5.2   |         | Exponentiation-Based Inversion                           |    |

|               | 5.3   |         | mentation Aspects and Results                            |    |

| 6             | Cor   | nclusio | ns                                                       | 83 |

| $\mathbf{Re}$ | feren | ices    |                                                          | 91 |

#### Abstract

Cryptography in its more general sense, is treating cryptosystem as a single-piece of software, mostly with the aim of encrypting/decrypting messages. The so-called black-box model captures the abstract security of a cryptosystem, but it does not consider the physical implementation, where the mathematical description of a function is actually performed by a device. In fact, physical implementations contradict the assumption over the intermediate computation not being accessible to the attacker. In the physical cryptanalysis model, new attacks became possible; and the Side-Channel Analysis (SCA) targets one of them: i.e. the leakage produced by the computation. In this thesis, we focused on the countermeasures required to prevent side-channel attacks.

In [ISW03], Ishai, Sahai and Wagner proposed a new formal model to protect algorithms from implementation leakage. And, since its appearance at CRYPTO 2003, the ISW model seemed to be a perfect fit to counter SCA; especially, because the authors provided the first probably secure construction in the side-channel area. At CHES 2010, Rivain and Prouff (RP) introduced an elegant masking technique to protect the AES against power analysis attacks. RP masking is provably secure in the probing model, but this solid theoretical underpinning comes at the cost of a massive increase in execution time. The ISW model, along with the RP masking implementation, provided the context where we funnel our researches.

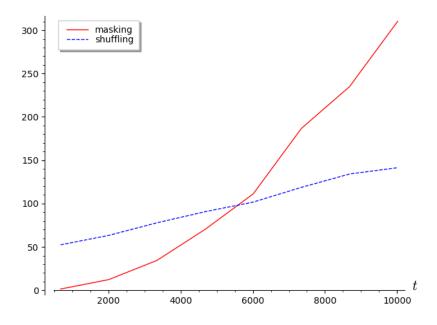

Our first contribution describes the first improvement of the wire shuffling countermeasure described in [ISW03]. More precisely, we show how to get worst case statistical security against t probes with running time  $\mathcal{O}(t)$  instead of  $\mathcal{O}(t \log t)$  (and  $\mathcal{O}(t^2)$  for the classical masking countermeasure); our construction is also much simpler to implement. We also provided a practical implementation for AES that outperforms the masking countermeasure for  $t \geq 6\,000$ .

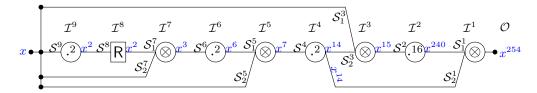

Our second contribution describes a software optimization methods to accelerate the lowlevel arithmetic in the field  $\mathbb{F}_{2^8}$ , which has a significant impact on the overall performance of a masked implementation of the AES. Among these optimizations is an improved technique for table-based multiplication in  $\mathbb{F}_{2^8}$  that allows one to avoid the special treatment of 0-values, thereby speeding up the multiplication of masked operands. Furthermore, we introduce a novel exponentiation-based algorithm for inversion in  $\mathbb{F}_{2^8}$ , which reduces the overall number of table look-ups and the amount of randomness needed for the refreshing of masks compared to the original RP inversion.

#### Introduction

Before introducing the *Side-Channel Analysis* (SCA), it might be useful to briefly go through the evolution of *Cryptography* in order to give an insight into the whole field and its terminology. We will retrace some of the milestones which drove this discipline to become as we know it today: from the historical to the modern approach, from the private-key to the public-key settings, and from the classical to the physical cryptanalysis.

#### 1.1 Historical vs Modern Cryptography

Leafing through modern dictionaries among many, there is a common definition that captures the essence of historical cryptography: "the art of writing or solving codes". In fact, at its very beginning, every attempt to describe cryptography was referred to as an *art*. This was due to the fact that the process of constructing or breaking codes relied exclusively on the ability of the cryptographer, who, indeed, had to develop a good knowledge of the codes mechanisms, however, the creativity of the individual was more crucial. Without any upon-agreed definition of what is meant to be "secure", encryption protocols were designed according to this mixture of creativity and ingenuity, and their security would be evaluated through an iterative process of searching for vulnerabilities and patching them ad hoc. This "artistic" approach seemed to be sufficient, considering that cryptography's initial application was limited to enabling two parties to communicate secretly, even in the presence of an eavesdropper who could monitor the exchange of messages between them. Moreover, such communicating parties were constituted predominantly by military organisations and governments, which, given the nature of the scope, were intended to keep the cryptography community as secret and restricted as possible. It is interesting to see how cryptographers were closer to illusionists than mathematicians in those early stages, focused more on misleading the eyes rather than dealing with theorems and proofs. Nevertheless, looking at it in retrospect, it is already possible to notice involuntary similarities with the *scientific method*; anticipating the modern evolution of the field as a proper *science* and a mathematical discipline.

1

The process that spotlighted this hidden nature lasted hundreds of decades and was characterised by several attempts, all considered secure a priori until the mechanisms behind them were exposed. This process of studying cryptographic systems to look for weaknesses or leaks of information is called *Cryptanalysis*, and it plays a crucial role even nowadays. Going in order, one of the oldest piece of evidence of encryption methods dates back to Julius Caesar in the last century CE. As established in De Vita Caesarum, Caesar used to cipher (i.e. encrypt) messages intended for his generals with the purpose of hiding the contents from his enemies. Julius Caesar's intuition was to use a "cyclically shifted" alphabet, where each letter is replaced by another letter located three places further in the alphabet; in this way, a message (also referred to as *plaintext*) like beginattacknow would have been sent as EHJLQDWWDFNQRZ (also referred as *ciphertext*), making it look like gibberish to anyone not aware of the encryption process. However, what was considered a "simple trick" leaded, centuries later, to a whole category of encryption schemes called *monoalphabetic substitution ciphers*, where each letter of the plaintext is replaced univocally with some other character according to a different logic. They were popular until a study about frequency analysis came out, breaking such cryptosystems. In fact, the study proposed by Al-Kindi showed a pattern between specific letters and their occurrence frequency in the language, making it easy to map each letter of the ciphertext with the corresponding one in the plaintext. In the 16th century, monoalphabetic ciphers were succeeded by *polyalphabetic substitution ciphers*: within the same cipher, the encryption algorithm alternated different monoalphabetic substitutions. The Vegenère's cipher is a famous example of this category, but it was also considered unbreakable for many years until an extension of the frequency analysis proved otherwise. In turn, in the 19th and 20th centuries, more advanced polyalphabetic ciphers appeared, which differed from the previous ones by their exploitation of mechanical devices. The Enigma machine belongs to this kind, and the Germans used it to encrypt radio communication during WWII. Enigma allowed the encoding of a message in billions of ways, making it incredibly difficult for other nations to crack German codes during the war and for a time the code seemed unbreakable. As we know from history, the Allies eventually broke Enigma, gaining the upper hand in the resolution of the conflict.

Moreover, cryptography propelled its transformation with the emergence of electronic devices and computers in the late 20th century. On one side, these new technologies speeded up complex computation in a reasonable time, allowing the design of more complex ciphers. In the 70s, a block cipher proposed by cryptographers at IBM was selected by the US National Bureau of Standards (NSA) as the first official Data Encryption Standard (DES); DES has been (and still is) widely used, analysed and improved since then. On the other side, the development of general-purpose computers extended the need for security beyond the governmental circles, capturing more and more attention, especially among mathematicians. These new large-scale consumers of cryptography pushed for a more rigorous approach, with the idealistic goal to provide the encryption scheme with a "certificate" (i.e. a *proof*) attesting its security. Consequently, the community began to see "mathematics" as a powerful mean to fill this scientific-approach gap. In fact, as we will see, Kerckoffs' law, Shannon's *information theory*, the *complexity theory* and other studies have influenced how researchers think about the broader field of computer security. In sum, cryptography has gone from a heuristic set of tools concerned with ensuring secret communication for the military to a science that helps secure systems for ordinary people all across the globe, forcing the field to evolve into a branch of applied mathematics and computer science.

An emphasis on definitions, assumptions and proofs distinguishes modern cryptography from classical. Those three principles are the foundations for whoever wants to approach the discipline, so it is worth briefly mentioning them. Formal definitions consist of a not ambiguous description of what threats must be prevented and what security guarantees must be achieved. A priori understanding of the security goal has been recognized as more effective than going the other way around. Additionally, it is interesting to notice that there are multiple (and all correct) ways to define security and the "better" definition exclusively depends on the context in which the scheme is deployed. In turn, a clear and exhaustive definition allows us to achieve the ultimate goal of producing security proofs. Such proofs act as a guarantee ensuring that no adversary can break the construction taken into consideration. Unfortunately, in practice, most cryptographic schemes cannot be proven unconditionally; otherwise, such proofs would be used to answer harder open questions from the computational complexity that seems far from being solved. Consequently, proofs of security typically rely on assumptions: some statement that is not proven but collectively conjectured to be true. As we said for the definitions, also for assumptions is challenging to define a scale, but clearly, older and long-studied assumptions should be preferred compared to new and ad hoc ones. Alternatively, as a general guideline, assumptions with a simple statement are often chosen too, since they are easier to study (or refute).

#### 1.2 Symmetric vs Asymmetric Cryptography

It is possible to divide modern cryptography into two main categories: Symmetric and Asymmetric. As implicitly described in the previous section, symmetric encryption involves using the same key for both encryption and decryption; the plaintext is encrypted depending on the key, and the same key is required to decrypt the ciphertext back to the original form. Hence, the key must be known in advance since it is used by both the sender and receiver. How such a key is securely exchanged remains out of the scope and is assumed to be already staged. For example, the secrecy of the "red line" used by the White House and the Kremlin during the Cold War was based on a symmetric-key encryption scheme called *One-Time Pad*, where a long key, written on paper and handily exchanged between the US and URSS emissaries, was applied. Clearly, whoever knows the key is able to encrypt or decrypt any message exchanged, so it is essential to keep it secret. Since the same key is used, symmetric cryptography is also referred to as *private-key* cryptography.

Most of the above-mentioned protocols, like the Caesar's and the Vegenère's ciphers, or the DES and all its variants, fall into the category. Despite being one of the oldest encryption techniques, symmetric schemes are still widely used today since they are faster and easier to implement compared to their asymmetric counterpart. This is due to several aspects that are still not achieved in asymmetric encryption: the ciphertext has the same length as the plaintext, the key shared by the parties hardly exceeds 128/256-bits and in most cases, the encryption phase requires a low-usage of resources. For such reasons and more, symmetric encryption is preferable in a context where a large amount of data needs to be encrypted and transmitted. Although, a few drawbacks balance the advantages from a theoretical point of view. The first has already been mentioned and it is an a priori assumption that the key has already been shared among the involved parties. Despite the problem, this brings to a slow-rate scaling, since sharing the same key with a new party must be carefully managed. Another relies on the fact that symmetric encryption suffers from key exhaustion issues; multiple usages of the same key over time may leak information about the key itself, which may lead an adversary to a complete reconstruction. Additionally, as we will see in full detail since it is the subject of the thesis, side-channel attacks can recover keys by exploiting the hardware characteristic of the devices where the protocol is running. Consequently, without appropriate key hierarchy and rotation, the probability of a breach represents a serious issue, especially for large-scale systems.

In opposition to symmetric, asymmetric cryptography enables parties to communicate privately without assuming that some secret information has already been shared. In asymmetric settings, the receiving party computes a *pair* of keys, one for the encryption phase (called the *public key*) and one for decrypting (called the *secret key*). Specifically, the public key is used by the sender to encrypt the plaintext. In contrast, the receiver requires the secret key to decrypt the ciphertext. Note that both keys are computed by the receiver and are independent of any specific senders. In this way, the receiver may publish its public key (say on its website or business card), and whoever wants to send a message can obtain the public key and proceeds with the ciphering; clearly, differently from the private-key settings, here, the roles in the exchange are not interchangeable: the receiver cannot reply using its keys, but it needs the sender's public key. This new way of exchanging messages marked a revolution in cryptography, allowing communication between parties to take place entirely through insecure channels. At the same time, in symmetric encryption protocols, the initial stage (i.e. the agreement on the secret key) can only occur via secure channels. On the flipping side, such a public key has to be assumed to be known by any attackers as well. For evident reasons, asymmetric cryptography is also referred to as public-key cryptography.

Hence, this new paradigm can overcome the significant disadvantage of private-key encryption: the issues related to the key distribution (at least to some extent). As explained, no data needs to be computed and agreed on during the process. For the same reason, asymmetric encryption is considered more secure and perfect for large-scale and "open" systems. Furthermore, public-key cryptography allows *digital signatures*, the digital equivalence of a handwriting signing on a paper document. This feature incorporates properties like *message authentication* and *non-repudiation* and has become an essential requirement nowadays; the private key is used to generate a signature which is hard to forge, and it identifies non- ambiguously a user while anyone may use the public key to confirm the signature of such user, as well as, once the user signed some data it is impossible to deny it afterwards. On the other side, these stronger security guarantees come at a price: efficiency. In fact, compared to private-key settings, public-key encryption requires very high resource utilization, mathematical time-consuming operations and large-sized keys, and it produces longer ciphertexts with respect to the initial plaintexts. In turn, if symmetric is preferable for the transmission of big chunks of data, the asymmetric counterpart is used to transfer a small amount of information.

As one last point, it may be interesting to underline the difference in how the two branches are evaluated and then considered secure. Usually, symmetric ciphers come with proofs of correctness, i.e. the decryption algorithm always returns the correct plaintext. While concerning the actual security, block-ciphers need to pass through years of unsuccessful cryptanalysis; in years, no attack can break the system has been found. Note that the attacks must be faster than an exhaustive search, which is always possible but at the rate of hundreds of years. Instead, asymmetric cryptosystems mostly rely on a hard problem from number theory, where the hardness is defined as the computational impossibility of finding a solution to the problem. Factorization of large prime numbers and discrete logarithm computation in multiplicative groups are the most used (but not the only ones) in modern cryptography. Here, the security proof is based on reduction; that is, claiming and proving that the existence of an adversary able to break the system would result in breaking the underlying hard problems.

#### 1.3 Black-Box Model vs Physical Cryptanalysis

So far, we have dealt with cryptography in its more general sense, treating a cryptosystem as a single piece of software, mainly intending to encrypt/decrypt messages. It evolved in more than that; a cryptosystem is essentially an algorithm implementing security services like confidentiality, integrity, authenticity and more. In turn, cryptosystems use *cryptographic primitives* as building blocks to achieve these specific security services. Cryptographic primitives are designed to compute some very specific task in a very precisely defined and highly reliable fashion.

Thus, cryptographic primitives are single components of larger and more complex systems. Hence, if a primitive is breakable, the whole system has to be considered breakable. On the other side, improving the security or the efficiency of primitives benefits the entire system. Nevertheless, both cryptosystems and primitives can be investigated in the same ways. The classical way is usually called black-box: in this model, protocols are assumed to be attacked by adversaries, which cannot exploit the inner structure of the primitives nor the intermediate computations of building blocks. That is, schemes are treated as oracles (i.e. black-boxes), where the adversary may query with inputs of its choice but obtain only the final output. Moreover, the security is evaluated according to the abilities of the adversary to query the oracle (un)bounded number of times, obtaining (un)bounded number of input/output pairs and still not recovering sensitive information from them. The black-box model captures the abstract security of a cryptosystem or a primitive but it does not consider the physical implementation, where the mathematical description of a function is actually performed by a device. In fact, physical implementations contradict the assumption of the intermediate computation not being accessible to the attacker. In practice, observations like the execution time, the power consumption or the electromagnetic radiation produced during the computation may be translated into actual intermediate values, giving the adversary information not considered in the black-box model. In the *physical cryptanalysis* model, new attacks became possible. They can be divided into two main categories: *fault analysis*, where the computation is disrupted, causing improper results, and *side-channel analysis*, considered the leakage produced by the computation. We will focus on the second category, where we funnelled our research.

#### 1.3.1 Side-Channel Analysis

As we mentioned, physical attacks take advantage of implementation-specifics characteristics to recover sensitive data. Therefore, this dependency on the specific implementation makes such attacks less general and, in turn, harder to contrast. Despite their peculiarity, the literature classified them as follows:

- 1. *Invasive attacks*: where a physical intervention on the device is required from the adversary. Namely, physically probe a wire of the device with a needle to observe the data passing through it.

- 2. Non-Invasive attacks: where the adversary exploits information unintentionally, but automatically, leaked by the device. Such external data are often running-time, power consumption etc.

- 3. Active attacks: where the attacker tries to intentionally jeopardise the correct functioning of the machine. As an example, fault-injections actively induce errors in the computation and observe the devise response.

- 4. *Passive attacks*: where the information leaked comes only from the act of observing the device's behaviour. Power analysis is the most common passive attack in which the power consumption of a device executing the algorithm is analysed to find the secret data.

However, the attacks most often considered in the literature are non-intensive and passive; i.e. timing information, power consumption and electric radiations. Moreover, the numerous range of attacks produced, joined with the exponential increase of software applications in our daily life, has turned side-channel attacks into a real and practical concern. For those reasons, we are going to summarize the state of the art of the discipline. Or at least, the state of art the that provided the humus for our research.

Hence, since their introduction in the late 90s, side-channel attacks have been under several investigations. Despite the numerous customised patches adopted against well-known physical attacks, a heavy effort has been made to develop protection strategies. Among them, one of the widely used relies on applying *secret sharing* at the implementation level; where any sensitive data x is manipulated as a set of n shares. The so-called high-order masking was first introduced in [CJRR99], but it gained popularity with the milestone publication [ISW03]

at CRYPTO in 2003. Ishai, Sahai and Wegner's strategies achieved provable security in the so-called *probing security model*. Ishai et al. proposed a high-order masking scheme for multiplication over  $\mathbb{F}_2$  in quadratic complexity; in other words, they worked in the boolean context. The ISW scheme was later used by Rivain and Prouff to pass from boolean to arithmetic masking, [RP10]. This extension to  $\mathbb{F}_{2^n}$  allowed to introduce an efficient masked implementation of AES. This represented a turning point since before their work all previous masking schemes were proved to be secure only for 1-order or 2-order. In fact, the randomized-table countermeasure [CJRR99] achieved security only against 1-order attacks; while the Schramm-Paar countermeasure [SP06], designed to resist any *n*-order attacks, has been successfully broken by a 3-order attack in [CPR07].

Thus, over the years, Rivain-Proof masking has been investigated and a lot of publications came out to improve the efficiency via different approaches; let's recall some of them. In [Cor14], Coron described a technique to mask look-up tables of block-cipher of any order. Moreover, in those years, a flaw in [RP10] has been discovered concerning the refreshing of the used randomness in the multiplication algorithm. Such flaw was spotted by the authors themself, joined with others, in [CGPZ16]; and definitively fixed in [BBD+16]. Actually, Barthe et al. have contributed with their work in [BBD+16], not only in proposing a secure way to refresh randomness but also in introducing a new stronger security definition called *strong non-interference*, now considered among the most appreciated security in literature, in the physical attacks context.

Hence, since the beginning, it has been noticed that the most challenging part of the masking process is the non-linear operations; while any linear function can be masked easily and in  $\mathcal{O}(n)$ , there is no way (so far) to mask non-linear functions in less the  $\mathcal{O}(n^2)$ . Thus, the total complexity is dependent on the number of non-linear multiplications involved in the polynomial evaluation. The work done by Coron, Roy and Vivek [CRV14] represents the current best-known generic method for this aim. Furthermore, an alternative to the ISW-based polynomial methods was proposed by Carlet, Prouff, Rivain and Roche in [CPRR15], where they introduced a so-called algebraic decomposition method that can express an S-box in terms of a polynomial of low-degree.

In conclusion, despite its popularity and the many improvements proposed by the community, high-order masking still implies a strong overhead and practical implementation limitations. We will show our new contributions in this area, both theoretical and practical, hoping to get to reduce the gap existing between academia and practical usage in the real world.

#### Preliminaries

In this chapter, we are going to recall the basic background mentioned in the rest of this thesis. We start by characterizing the notion of circuits (see Section 2.1) and introducing the masking countermeasure (see Section 2.2). Then, we describe the operations performed by the encryption scheme AES (see Section 2.3).

#### 2.1 Circuits

As in [ISW03], we consider probing attacks mainly in the setting of circuits. A deterministic circuit C can be pictured as a directed acyclic graph, where gates are represented as vertices and the wires are expressed as edges. As a well-established practice, we also assume that every gate has fan-in and fan-out at most 2. Note that this will not imply a loss in the generality since it is always possible to transform any circuit with general fan-in/fan-out in one belonging to the above type, with a logarithmic cost in the depth. Moreover, a random-bit gate is a gate having no inputs (i.e. fan-in 0) and outputting a random bit, that is sent along its output wire; the bit is selected uniformly and independently. The size of a circuit, denoted by |C|, is the number of gates, while its depth is defined as the length of the longest path from an input to an output. We refer to a circuit just described as a *stateless* circuit.

In contradistinction, a *stateful* circuit is a stateless circuit but augmented with memory cells. A memory cell is a gate with fan-in and fan-out 1, that, on any invocation, outputs the previous input to the gate, and stores the current input for the next invocation. In other words, a memory cell acts as a delay element. When C denotes a stateful circuit, it is required that such circuit is initialized with some initial state  $s_0$ ; usually,  $C[s_0]$  is used to indicate a circuit C with memory cells initially filled with  $s_0$ . Stateful circuits can also have external input and output wires.

$\mathbf{2}$

#### 2.2 Masking Countermeasure

As mentioned in the previous chapter, SCA attacks are based on the observation of a set of intermediate variables (say, for example, t) computed during a cryptosystem processing. One of the most used and studied techniques is the randomization of the cryptosystem in such a way that the probability distribution of any subset of at most t intermediate computations is independent of the secret key. In order to achieve this randomization, it is applied to the data of the circuit what has been called the *masking countermeasure*, [CJRR99]. In a nutshell, this technique maps any sensitive variable x (i.e a variable that depends on some required-secret information) into n shares  $x_1, x_2, \ldots, x_n$  satisfying the following equation:

$$x_1 \oplus x_2 \oplus \ldots \oplus x_n = x \tag{2.1}$$

Often the first n-1 shares (also called masks) are initially assigned uniformly at random, while  $x_n$  is computed as  $x_n = x \oplus x_1 \oplus \ldots \oplus x_{n-1}$  to maintain the validity of Equation (2.1). Furthermore, the term *order* of the masking is identified as the number of shares generated at random; for instance, if we take the above masking in the examination, we would say that it is an (n-1)-order masking. In literature, sometimes the order has been also referred to as d; but, in this thesis, to avoid confusion, we will mostly stick to the notation "n" for the number of shares and "n-1" for the order. The main guarantee provided by an (n-1)-order masking is that every (n-1)-tuple of intermediate variables is statistically independent of the secret key.

When the masking is applied to some cryptosystem, the challenge is to deal with the shares of x and not with x itself; each operation must be redesigned to manipulate shares while the input-output functionality is maintained. On one side, linear operations are straightforward to mask since they can be computed independently and at the shares-level (i.e. between shares with the same index). That is, for every linear function f the following equation is held:

$$f(x_1) \oplus f(x_2) \oplus \ldots \oplus f(x_n) = f(x_1 \oplus x_2 \oplus \ldots \oplus x_n)$$

(2.2)

On the flipping coin, properly masking non-linear functions (like boolean or arithmetic multiplication or implementation of the S-box used in AES, see Section 2.3) is a harder task. How to compute those non-linear functions has a crucial role, in fact, it will imply how fast, how efficient and how secure the masked cryptosystem is; making it more or less practical in the real world.

Concerning, again, the notation adopted in this thesis, we would like to remark to the reader that the set of shares or masks will mainly be referred to as a vector  $\mathbf{x} = (x_1, x_2, \ldots, x_n)$  or as a set  $(x_i)_{1 \le i \le n}$ ; moreover, sometimes we will refer to a specific subset of shares with the notion  $x|_I := (x_i)_{i \in I}$ , meaning only the shares whose index belongs to the set I must be considered.

#### 2.3 Advanced Encryption Standard

The block cipher Rijndael was selected by NIST in 2001 to become the encryption standard called *Advanced Encryption Standard* (or AES) [DR02]. We are going to briefly recall its structure. It might be useful to start from the difference between Rijndael, proposed by Deamen and Rijmen, and the final accepted standard AES. Such disparities only involve the range of parameters in the length of both blocks and key applicable to the cryptosystem. Concretely, while Rijndael allows every multiple of 32 bits in the range [128, 256] bits; AES supports only blocks of fixed length 128 bits with a key that may be 128, 192 or 256 bits long.

#### 2.3.1 Specifications of Rijndael

The Rijndael block cipher is structured as a multiple rounds transformation. Such transformations are applied to what they have called the *state*: one-dimensional arrays of 8-bit bytes. Where the input state is the plaintext and the output state is the ciphertext. The state is usually represented as a  $4 \times N_b$  matrix, where  $N_b$  is the number of columns (computed as the block length divided by 32); symmetrically, the key is represented as a  $4 \times N_k$  matrix, where  $N_k$  is the number of columns (computed as the key length divided by 32). See Figure 21 for an illustration. Note that, even if we have displayed the state and the key in their array notation (i.e.  $s_0, s_1, s_2, \ldots, s_{4\cdot N_b}$  and  $k_0, k_1, k_2, \ldots, s_{4\cdot N_k}$ ), sometimes, for convenience, we will use the matrix notation of the elements (i.e.  $s_{i,j} \ 0 \le i \le 4 \cdot N_b$  and  $k_{i,j} \ 0 \le i \le 4 \cdot N_k$ ).

| 1 | $\langle s_0 \ s_4 \ s_8 \ s_{12} \rangle$ | $k_0$ | $k_4$ | $k_8$    | $k_{12}$ | $k_{16}$ | $k_{20}$ |

|---|--------------------------------------------|-------|-------|----------|----------|----------|----------|

|   | $s_1 \; s_5 \; s_9 \; s_{13}$              | $k_1$ | $k_5$ | $k_9$    | $k_{13}$ | $k_{17}$ | $k_{21}$ |

|   | $s_2 \ s_6 \ s_{10} \ s_{14}$              | $k_2$ | $k_6$ | $k_{10}$ | $k_{14}$ | $k_{18}$ | $k_{22}$ |

|   | $(s_3 \ s_7 \ s_{11} \ s_{15})$            | $k_3$ | $k_7$ | $k_{11}$ | $k_{15}$ | $k_{19}$ | $k_{23}$ |

Fig. 21: State and Key layout for  $N_b = 4$  and  $N_k = 6$ .

For each element (i.e byte), the authors used the polynomial representation of  $\mathbb{F}_{2^8}$ . Namely, in the scheme, each  $s_{i,j}$  and  $k_{i,j}$  is treated as a polynomial of a degree smaller the 8, with a coefficient in  $\mathbb{F}_2$ . Moreover, the multiplication has been chosen to work modulo the irreducible polynomial  $m(x) = x^8 + x^4 + x^3 + x + 1$ . As mentioned at the beginning of the Section, Rijndael consists of an iterated application of a round transformation. The number of rounds is fixed and determined according to the block and key length, we refer to it as N<sub>r</sub>. In practice, such values are specified in Figure 22.

| N <sub>b</sub><br>N <sub>k</sub> | 4  | 5  | 6  | 7  | 8  |

|----------------------------------|----|----|----|----|----|

| 4                                | 10 | 11 | 12 | 13 | 14 |

| 5                                | 11 | 11 | 12 | 13 | 14 |

| 6                                | 12 | 12 | 12 | 13 | 14 |

| 7                                | 13 | 13 | 13 | 13 | 14 |

| 8                                | 14 | 14 | 14 | 14 | 14 |

Fig. 22: Number of Rounds of Rijndael. Note that for AES  $N_b$  is fixed to 4 and  $N_k \in \{4, 6, 8\}$ .

In a nutshell, each round is a composition of the following operations:

1. SubBytes: is the only non-linear transformation of the cipher. This transformation consists of a specific S-box applied to the state. Such S-box is designed to achieve non-linearity (minimizing the maximum input-output correlation amplitude and the maximum difference propagation probability) and algebraic complexity. The chosen S-box is defined by the following function in  $\mathbb{F}_{2^8}$ :

$$SB_8: a \to Aff_8(Inv_8(a))$$

(2.3)

Where  $Inv_8$  is defined in Equation (2.4) and it is the inversion function in the field;

$$Inv_8: a \to a^{-1} \tag{2.4}$$

while  $Aff_8$  is an invertible affine transformation produced from a polynomial multiplication XORed with a constant and is defined in Equation (2.5):

$$\operatorname{Aff}: a \to \left( \begin{array}{ccccccccc} 1 & 1 & 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 1 \\ 1 & 0 & 0 & 0 & 1 & 1 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 & 1 & 1 & 1 \\ 1 & 1 & 1 & 0 & 0 & 0 & 1 & 1 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 1 \end{array} \right) \times a) \oplus \begin{bmatrix} 0 \\ 1 \\ 1 \\ 0 \\ 0 \\ 0 \\ 1 \\ 1 \end{bmatrix} \tag{2.5}$$

2. ShiftRows: is a byte transposition that cyclically shifts the rows of the state over different offsets (respectively 0, 1, 2 and 3 for the first, second, third and fourth row); see Figure 23. Such offsets are chosen to achieve optimal diffusion to maximal resistance against truncated differential attacks.

| $\left(s_0 \ s_4 \ s_8 \ s_{12}\right)$ |               | $(s_0)$    | $s_4$    | $s_8$    | $s_{12}$ |

|-----------------------------------------|---------------|------------|----------|----------|----------|

| $s_1 \; s_5 \; s_9 \; s_{13}$           | $\rightarrow$ | $s_5$      | $s_9$    | $s_{13}$ | $s_1$    |

| $s_2 \; s_6 \; s_{10} \; s_{14}$        |               | $s_{10}$   | $s_{14}$ | $s_2$    | $s_6$    |

| $(s_3 \ s_7 \ s_{11} \ s_{15})$         |               | $(s_{15})$ | $s_3$    | $s_7$    | $s_{11}$ |

Fig. 23: The input state (right) vs ShiftRows's output state.

3. MixColumns: is a permutation of the state column by column. The columns of the state are multiplied by the polynomial  $3x^3+x^2+x+2 \mod x^4+1$ , see Figure 24. The polynomial has been chosen considering dimension, linearity, diffusion and performance on 8-bit processors.

| $[2 \ 3 \ 1 \ 1]$                             |        | $s_{4\cdot i}$     |

|-----------------------------------------------|--------|--------------------|

| 1231                                          | $\sim$ | $s_{(4\cdot i)+1}$ |

| 1 1 2 3                                       | X      | $s_{(4\cdot i)+2}$ |

| $\begin{bmatrix} 3 \ 1 \ 1 \ 2 \end{bmatrix}$ |        | $s_{(4\cdot i)+3}$ |

Fig. 24: The multiplication of the polynomial  $3x^3 + x^2 + x + 2 \mod x^4 + 1$  is performed per each column of the state, i.e for  $1 \le i \le 4$ .

4. AddRoundKey: is a XORing operation between the state and RoundKey, namely each round uses its own round key. The array of round keys (called ExpandedKey[]) comes from a key schedule procedure taking as input the key of the cipher and, according to the length of the key see Algorithm 2.1 and Algorithm 2.2, returns an array of N<sub>k</sub> RoundKeys. The size of the ExpandedKey is equal to the block length multiplied by the number of rounds.

$$egin{pmatrix} & (s_0 \ s_4 \ s_8 \ s_{12} \ s_1 \ s_5 \ s_9 \ s_{13} \ s_2 \ s_6 \ s_{10} \ s_{14} \ s_3 \ s_7 \ s_{11} \ s_{15} \end{pmatrix} \oplus egin{pmatrix} k_0^{(r)} \ k_4^{(r)} \ k_4^{(r)} \ k_8^{(r)} \ k_{12}^{(r)} \ k_{12}^{(r)} \ k_{13}^{(r)} \ k_{13}^{(r)} \ k_{13}^{(r)} \ k_{13}^{(r)} \ k_{13}^{(r)} \ k_{14}^{(r)} \ k_{14}^{(r)} \ k_{14}^{(r)} \ k_{14}^{(r)} \ k_{14}^{(r)} \ k_{14}^{(r)} \ k_{15}^{(r)} \ k_{11}^{(r)} \ k_{15}^{(r)} \end{pmatrix}$$

Fig. 25: The input state (right) is XORed with the key computed by ExpandedKey for the r-th round, with  $1 \le r \le N_r$ .

#### **Algorithm 2.1** KeyExpansion - for $N_k \leq 6$

Input: CipherKey: K[4][N<sub>k</sub>]; S-box: SB[256]; RC: [1,0,0,0].  $\mathbf{Output:} \ \mathsf{ExpandedKey:} \ \mathsf{W}[4][\mathsf{N}_{\mathsf{b}}(\mathsf{N}_{\mathsf{r}}+1)]$ 1: for j = 0 to  $N_r - 1$  do for i = 1 to 3 do 2: 3:  $\mathsf{W}[i][j] \leftarrow \mathsf{K}[i][j]$ 4: for  $j = N_k$  to  $N_b(N_k + 1) - 1$  do if  $j \mod N_k = 0$  then 5:6:  $\mathsf{W}[0][j] \leftarrow \mathsf{W}[0][j-\mathsf{N}_{\mathsf{k}}] + \operatorname{SB}[\mathsf{W}[0][j-1]] + \operatorname{RC}[j/\mathsf{N}_{\mathsf{k}}]$ 7:for i = 1 to 3 do 8:  $\mathsf{W}[i][j] \leftarrow \mathsf{W}[i][j-\mathsf{N}_{\mathsf{k}}] + \operatorname{SB}[\mathsf{W}[i+1 \mod 4][j-1]]$ 9: else10: for i = 0 to 3 do 11:  $W[i][j] \leftarrow W[i][j - N_k] + W[i][j - 1]$ 12: return W

**Algorithm 2.2** KeyExpansion - for  $N_k > 6$

```

Input: CipherKey: K[4][N<sub>k</sub>]; S-box: SB[256]; RC: [1,0,0,0].

Output: ExpandedKey: W[4][N_b(N_r + 1)]

1: for j = 0 to N_r - 1 do

for i = 1 to 3 do

2:

3:

W[i][j] \leftarrow K[i][j]

4: for j = N_k to N_b(N_k + 1) - 1 do

5:

if j \mod N_k = 0 then

\mathsf{W}[0][j] \leftarrow \mathsf{W}[0][j-\mathsf{N}_{\mathsf{k}}] + \operatorname{SB}[\mathsf{W}[0][j-1]] + \operatorname{RC}[j/\mathsf{N}_{\mathsf{k}}]

6:

7:

for i = 1 to 3 do

\mathsf{W}[i][j] \leftarrow \mathsf{W}[i][j - \mathsf{N}_{\mathsf{k}}] + \operatorname{SB}[\mathsf{W}[i+1 \mod 4][j-1]]

8:

else if j \mod N_k = 4 then

9:

for i = 0 to 3 do

10:

\mathsf{W}[i][j] \leftarrow \mathsf{W}[i][j - \mathsf{N}_{\mathsf{k}}] + \operatorname{SB}[\mathsf{W}[i][j - 1]]

11:

12: return W

13:

else

14:

for i = 0 to 3 do

15:

W[i][j] \leftarrow W[i][j - N_k] + W[i][j - 1]

16: return W

```

In conclusion, we recall the algorithm: the procedure starts with the expansion of the key and the first XOR between the initial state and the cipher key follows. Afterwards, the algorithm iterates the round procedure for  $N_r - 1$  times, since the last round is composed slightly differently. Namely, for the last round, the MixColumn is removed, as it adds no security to the cipher since it can be trivially inverted. See Algorithm 2.3 for the details.

| Algorithm 2.3 AES - Encryption protocol |  |  |  |  |

|-----------------------------------------|--|--|--|--|

| $\mathbf{Rijndael}(State,CipherKey)$    |  |  |  |  |

| KeyExpansion(CipherKey, ExpandedKey)    |  |  |  |  |

| AddRoundKey(State,ExpandedKey[0])       |  |  |  |  |

| for $i = 1$ to $N_r - 1$ do             |  |  |  |  |

| SubBytes(State)                         |  |  |  |  |

| ShiftRows(State)                        |  |  |  |  |

| MixColumn(State)                        |  |  |  |  |

| AddRoundKey(State,ExpandedKey[i])       |  |  |  |  |

| SubBytes(State)                         |  |  |  |  |

| ShiftRows(State)                        |  |  |  |  |

| $AddRoundKey(State,ExpandedKey[N_r])$   |  |  |  |  |

*Remark 2.1.* In this section, only the encryption phase has been considered since the decryption is straightforward. In fact, note that each of the above operations is easily invertible and for

this reason they have been omitted. Nevertheless, we refer the reader to [DR02] for the inverted variant of the above functions, as well as, the decryption algorithm and the security proofs.

#### Side-Channel Analysis

In this chapter, we are going to see in detail some of the publications mentioned in the Introduction. More specifically, we face the state of the art that is at the bottom of the contributions proposed in this thesis and done in those four years. From the ISW model (see Section 3.1) to the first proven secure masked implementation of AES (see Section 3.2). Introducing the SNI security (see Section 3.3). Lastly, we describe the models considered in our works: the regional probing model (see Section 3.4) and the software probing model (see Section 3.5).

#### 3.1 The ISW Model

In [ISW03], Ishai, Sahai and Wagner showed a new formal model to protect primitives from implementation leakage, but from a designing point of view. Their work had the aim of proposing new security definitions to guarantee an inherent resistance against a large class of side-channel attacks. The goal was to build protection for generic probing attacks. To achieve the generic characteristic, the approach was to ignore how the information leaks but to focus on predicting how much and at what rate the information is going to leak. Moreover, their model is generic in the sense that privacy is ensured for any cryptosystem or primitive. Consequently, the authors reasoned in terms of circuits; in particular, they showed how to transform any circuit into a different and larger one, where security is guaranteed even in presence of an attacker observing a bounded amount of wires. In other words, the ISW model provided definitions of security against probing attacks and constructions that are proven to achieve such definitions.

The impossibility of achieving obfuscation, presented in [BGI<sup>+</sup>01], forced some limitation in the power of the attacker considered in their definitions. In fact, the result in [BGI<sup>+</sup>01] can be extended to any adversary probing any internal computation. The limitation introduced in their paper was defined as a parameter: in their model, they considered attackers that can observe or probe up to t wires in the examined circuit within one clock cycle. Nevertheless, such a t-limited adversary sounded like a reasonable restriction either considering the fact that in practice almost all known side-channel attacks are able to recover just part of the information or taking into account that a single physical probe is performed through a very expensive needle, making a bound over the number of probes that a real-world attacker can afford. Finally, it is interesting to stress that no theoretical model formulation, before [ISW03], had ever achieved *provable* security. The authors defined security in terms of *transformers T*: an efficiently computable randomized algorithm taking as input a circuit C and returning a different circuit C'. In addition, such C' needs to encounter some properties: that is C' needs to satisfy *soundness* and *privacy* to be considered *t*-private. The several definitions given in [ISW03] differ from each other according to how soundness and privacy are stated; in turn, they are characterized by: 1) the type of the examined circuit, i.e. stateless or stateful and 2) the straight of the privacy guarantees, i.e. perfect, statistical or computational.

In the following subsections, we are going to recall definitions, constructions and proofs for the perfect privacy in stateless (Section 3.1.1) and stateful (Section 3.1.2) settings; then we will introduce the random probing model (Section 3.1.3) since it is essential to understand definitions, constructions and proofs for the statistical privacy in stateless (Section 3.1.4) and stateful (Section 3.1.5) setting.

#### 3.1.1 Perfect Privacy for Stateless Circuits

**Definition.** Informally, to achieve perfect privacy for stateless circuits there must exist a transformer able to take any circuit C and compute it in order to output a new circuit C', where the input-output functionality of C and C' are identical for any distinguisher and any adversary being able to probe up to t internal wires of C' would learn nothing from those values. In addition, the original input and output of C should be kept hidden. In order to satisfy this requirement, the transformer can make use of a randomized *input encoder* I and an *output decoder* O. Both I and O cannot be accessed (or probed) by the adversary and they need to be designed to be independent of the circuit C. Note that the assumption of not being probed for the encoder/decoder can be easily obtained in practice too; since typically such circuit needs very few gates to be computed, they may be implemented by temper-resistant hardware components, where the expensive cost is balanced by the small size. Formally:

**Definition 3.1 (Perfect privacy for stateless circuits [ISW03]).** Let T be an efficiently computable deterministic function mapping a stateless circuit C to a stateless circuit C', and let I, O be as above. We say that (T, I, O) is a t-private stateless transformer if it satisfies the:

- 1. Soundness. The input-output functionality of  $O \circ C' \circ I$  (i.e., the iterated application of I, C', O in that order) is indistinguishable from that of C.

- 2. **Privacy.** It is required that the view of any t-limited adversary, which attacks  $O \circ C' \circ I$  by probing at most t wires in C', can be simulated from scratch, i.e. without access to any wire in the circuit. The identity of the probed wires has to be chosen in advance by the adversary.

**Construction.** In [ISW03], the authors presented their construction to achieve perfect privacy in the stateless setting. As formalized below, they used a simple secret-sharing scheme, this technique is often referred to as masking countermeasure. The idea is to deal with every intermediate variable x as n shares  $x = x_1 \oplus x_2 \oplus \cdots \oplus x_n$  and process each  $x_i$  separately along the circuit. As a consequence, the gates have to be carefully computed in such a way that intermediate computations do not leak sensitive information. For security against t probes, the three algorithms (I, T, O) require n = 2t + 1 shares; and they are defined as follows:

- Encode *I*. Each binary input *x* is mapped to *n* binary values. First, n 1 random bits  $r_1, \ldots, r_{n-1}$  are independently generated. The encoding of *x* is composed of these n 1 random values together with  $r_n = x \oplus r_1 \oplus \ldots \oplus r_{n-1}$ . The circuit *I* computes the encoding of each input bit independently.

- Decode O. The output returned by T(C) has the form  $y_1, \ldots, y_n$ . The associated output bit of C computed by O is  $y_1 \oplus \ldots \oplus y_n$ .

- Transformer T. Assume without loss of generality that the original circuit C consists of only XOR and AND gates. The transformed circuit C' maintains the invariant that corresponding to each wire in C will be n wires in C' carrying an n-sharing of the value on that wire of C. More precisely, the circuit C' is obtained by transforming the gates of C as follows.

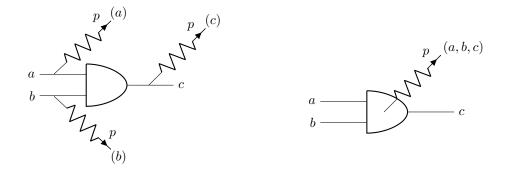

For an XOR gate with inputs a, b and output c, let in C' be the corresponding wires  $a_1, \ldots, a_n$  and  $b_1, \ldots, b_n$ . From  $c = a \oplus b = \bigoplus_{i=1}^n a_i \oplus b_i$ , we let  $c_i = a_i \oplus b_i$  for  $1 \le i \le n$ . Consider an AND gate in C with inputs a, b and output c; we have  $c = a \land b = \bigoplus_{i,j} a_i b_j$ . In the transformation of this gate, intermediate values  $z_{i,j}$  for  $i \ne j$  are computed. For each  $1 \le i < j \le n, z_{i,j}$  is computed uniformly random, while  $z_{j,i}$  is set to  $(z_{i,j} \oplus a_i b_j) \oplus a_j b_i$ . Now, the output bits  $c_1, \ldots, c_n$  in C' are defined to be the sequence  $c_i = a_i b_i \oplus \bigoplus_{j \ne i} z_{i,j}$ .

Remark 3.2. We would like to remark that in the original paper [ISW03] the description of the transformer was considering circuits composed of only NOT and AND gates; differently from them, we preferred to work with only XORs and ANDs. Nevertheless, the two descriptions of circuits are equivalent. Intuitively, they processed the NOT gate simply by maintaining the first n-1 wires as they are and putting an inverter after the *n*-th wire.

Since it will be helpful later, we also provided an algorithmic description of AND in Algorithm 3.1. In the transformed circuit C' = T(C), every XOR gate and AND gate in C are therefore expanded to gadgets of size  $\mathcal{O}(n)$  and  $\mathcal{O}(n^2)$  respectively, and the gadgets in C' are connected in the same way as the gates in C. This completes the description of T.

**Algorithm 3.1** AND gadget - *d*-order secure multiplication over  $\mathbb{F}_2$

**Input:** shares  $a_i$  satisfying  $\bigoplus a_i = a$ , shares  $b_i$  satisfying  $\bigoplus b_i = b$ **Output:** shares  $c_i$  satisfying  $\bigoplus c_i = a \cdot b$ 1: for i = 1 to n do 2: for j = i + 1 to n do 3:  $r_{i,j} \xleftarrow{\$} \{0,1\}$  $r_{j,i} \leftarrow (r_{i,j} \oplus a_i b_j) \oplus a_j b_i$ 4: 5: for i = 1 to n do 6:  $c_i \leftarrow a_i b_i$ 7: for  $(j = 1 \text{ to } n) \land (i \neq j)$  do 8:  $c_i \leftarrow c_i \oplus r_{i,j}$ 9: return  $(c_1, ..., c_n)$

**Security.** As said previously, one of the strongest points of the ISW model is the fact that it is provably secure. Thus, the authors could provide proof that the above construction is indeed perfectly *t*-private in the stateless setting as stated in the following. We will give a scratch of the proof proposed in [ISW03] but we refer the reader to the original paper for a detailed explanation.

**Theorem 3.3.** The above construction is a perfectly t-private stateless transformer (T, I, O), such that T maps any stateless circuit C of depth d to a randomized stateless circuit of size  $\mathcal{O}(|C| \cdot t^2)$  and depth  $\mathcal{O}(d \log t)$ .

Proof (Scratch of the proof). In order to prove the theorem, the authors had to show that the construction achieves soundness and privacy. If it should be easy to verify that C and C' have the same input-output functionality, proving the privacy requires a bit more effort. Specifically, it implies generating values for the t probes chosen by the adversary and making them indistinguishable from the ones the attacker would have obtained in a real execution of C'. In addition, such t queries have to be provided without any knowledge of the input of C. The term *simulator* indicates the algorithm computing from scratch the t values for the probes.

The proof starts proving the *t*-privacy for a *single* gadget: the goal is to carefully define a set of input wires indices  $\mathcal{I}$  such that the joint distribution of values assigned to the probed wires can be simulated from the  $a_i$ s and  $b_i$ s belonging to  $\mathcal{I}$ . This would be enough to ensure privacy since, by definition, the input shares  $\{a_i\}$  and  $\{b_i\}$ , as well as the output shares  $\{c_i\}$ , have the property that any n-1 subset of such shares are distributed as uniformly random, thus, assigning random values to  $a_i|_{\mathcal{I}}$  and  $b_i|_{\mathcal{I}}$  (and computing the probes accordingly to them) would allow an indistinguishable view as long as the cardinality of  $\mathcal{I}$  is not exceeding n-1 elements. Hence, first set  $\mathcal{I}$  is defined: supposing the adversary has probed  $w_1, w_2, \ldots, w_t$ , each

$w_h$  can carry only a few values, i.e  $a_i, b_i, a_i b_i, z_{i,j}^1$  or any sum among them,  $a_i b_j, z_{i,j}^1 \oplus a_i b_j$ and  $c_i$ . The procedure is the following:

- 1. If  $w_h$  is in the form  $a_i, b_i, c_i, a_i b_i, z_{i,j}$  or any sum among them, then index *i* is added to  $\mathcal{I}$ .

- 2. If  $w_h$  is in the form  $a_i b_j$  or  $z_{i,j} \oplus a_i b_j$ , then both indices i and j are added to  $\mathcal{I}$ .

Note that in both cases for each probe  $w_h$  up to two indices are added to  $\mathcal{I}$ , so it holds that  $|\mathcal{I}| \leq 2t < n$  as required. Now, after composing the set of indices, proofs state how to simulate every type of probe:

- If  $w_h = a_i, b_i, a_i b_i$  then  $i \in \mathcal{I}$  and a uniform random assignment perfectly simulates them.

- The  $w_h = z_{i,j}$  case needs a bit more attention since we can have more than one case: 1)  $i \notin \mathcal{I}$ , then, independently from j,  $z_{i,j}$  is not part of any  $w_h$  and it can be unassigned; 2)  $i \in \mathcal{I} \land j \notin \mathcal{I}$ , then  $z_{i,j}$  is assigned a random value, it perfectly simulates it since  $j \notin \mathcal{I}$ guarantees that no  $w_h$  is using  $z_{i,j}$  where i > j, and otherwise if i < j C' would have assigned a random value anyway; 3)  $i \in \mathcal{I} \land j \in \mathcal{I}$ , then  $z_{i,j}$  is computed as it would be in C' since  $a_i$ ,  $b_i$ ,  $a_j$  and  $b_j$  have been already perfectly simulated.

- If  $w_h = a_i b_j$ ,  $z_{i,j} \oplus a_i b_j$ ,  $c_i$  then it can be perfectly simulated from the previous two assignment, proving the *t*-privacy for a single gadget.

To conclude the proof, the security is extended to the entire circuit and it proceeded very similarly to the single gadget. In particular, they looked at the circuit as a subsequence of gadgets going from the inputs to the outputs of  $C': G_1, G_2, \ldots, G_{|C'|}$ . Then, each gadget is examined and a unique set  $\mathcal{I}$  of indices is computed as described above and the probes are simulated from  $a_{|\mathcal{I}|}$  and  $b_{|\mathcal{I}|}$  in the same way aforementioned. The *t*-privacy still holds since the bound on the number of corrupted wires is applied to the entire circuits and they cannot exceed *t*; in this way the set  $\mathcal{I}$  would maintain cardinality less than *n*. Consequently, the perfect simulation can be extended to C'.

#### 3.1.2 Perfect Privacy for Stateful Circuits

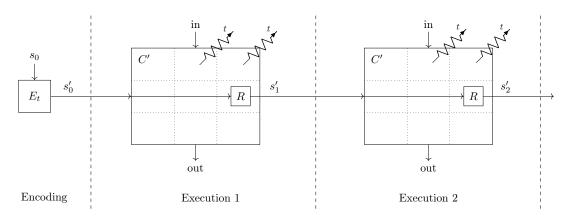

**Definition.** As it was for the stateless setting, privacy is defined in terms of a transformer T mapping a stateful circuit C, including its initial state  $s_0$ , into a new stateful circuit C' with a new initial state  $s'_0$ . Moreover, differently from the stateless counterpart, they considered the circuit inputs and outputs to be public, i.e. only the internal state is kept private. The adversary can now access the transformed circuit and invoke it multiple times, choosing freely the new invocation inputs; the adversary may choose the next input based on what it has observed in the previous execution. The stateful case is, surely, a stronger and more realistic model to use in practice; however, as we will see, the construction will exploit the private transformer from the stateless circuits, since it will make it easy to prove stateful privacy once the stateless security has already been achieved. Formally:

<sup>&</sup>lt;sup>1</sup> For some  $i \neq j$ .

**Definition 3.4 (Perfect privacy for stateful circuits [ISW03]).** Let T be an efficiently computable randomized algorithm mapping a stateful circuit C along with an initial state  $s_0$  to a stateful circuit C' along with an initial state  $s'_0$ . We say that T is a t-private stateful transformer if it satisfies the:

- 1. Soundness. The input-output functionality of C initialized with  $s_0$  is indistinguishable from that of C' initialized with  $s'_0$ . This should hold for any sequence of invocations on an arbitrary sequence of inputs. In other words,  $C[s_0]$  and  $C'[s'_0]$  are indistinguishable to an interactive distinguisher.

- 2. **Privacy.** We require that C' be private against a t-limited interactive adversary. Specifically, the adversary is given access to C' initialized with  $s'_0$  as its internal state. Then, the adversary may invoke C' multiple times, adaptively choosing the inputs based on the observed outputs. Prior to each invocation, the adversary may fix an arbitrary set of t internal wires to which it will gain access in that invocation. To define privacy against such a t-limited adversary, we require the existence of a simulator which can simulate the adversary's view using only black-box access to C', i.e., without having access to any internal wires.

**Construction.** The ISW construction for perfect privacy in the stateful model proceeds as follows: they made use of the stateless transformer T(C, t) from Theorem 3.3 to secure every gate of the original circuit C while ensuring privacy for the memory cell requires a different approach. This is due to the adaptivity of the adversaries in the stateful context. Namely, as said previously, the attacker can now move the probes between executions and choose adaptively the input. To overcome this power of the adversary, each memory cell in C will be encoded using I (as described in Section 3.1.1): let denote by  $E_t(x)$  such encoding, where x is the input being encoded and t its probing tolerance (that is the shares of  $E_t(x)$  are t-wise independent). Thus, the stateful transformer is defined as  $T = (T_C, T_s)$ :  $T_C$  is the stateless transformer from above and it would be applied to every gate, while  $T_s$  is an encoding  $E_{2t}(s_i)$ and it would be applied to every memory cell  $s_i$ . In addition, C' is built to consider the encoding of the initial state  $E_{2t}(s_0)$  as an input and every next state of the memory is always returned as an output. Note that encoding against 2t is crucial to guarantee the t-privacy: in this model, the adversary could have probed t input shares of the memory cell in one execution and probe t output shares of the same memory cell in the next execution; in the stateful construction it is a necessary protection against 2t probes. Consequently, the number of shares used in the stateful setting rise to n = 4t + 1 for tolerance to 2t corruptions.

Security. Perfect privacy in the stateful model follows very similarly to perfect privacy in the stateless setting. In particular, it is possible to look at multiple invocations of the stateful C' as an unwound larger stateless circuit Q, where the input-output functionality is maintained. In this way, the proof would go like before with the only difference that in Q inputs and outputs are hidden while in C' they are given to the adversary; nevertheless, those values can be passed to the simulator and can be easily incorporated into the simulation. The proof from Theorem 3.3 would perfectly simulate the internal probes, while the memory corruptions can

be simulated by assigning random values due to the *re-randomization* property: each of the concatenated invocations in Q has outputs that are *t*-wise independent if conditioned to its input values. That is enough to prove the following:

**Theorem 3.5.** The above construction is a perfectly t-private stateful transformer (T, I, O), such that T maps any stateful circuit C of depth d to a randomized stateful circuit of size  $\mathcal{O}(|C| \cdot t^2)$  and depth  $\mathcal{O}(d \log t)$ .

#### 3.1.3 Random Probing Model

As mentioned in Section 3.1, the authors relaxed the perfect security in order to improve the running time of the above constructions. In fact, the major disadvantage of the perfect security is their complexity grows quadratically in the number of shares (and, in turn, in the number of probes): for both stateless and stateful models the overall running time is  $\mathcal{O}(|C|t^2)$ . The improvement in time complexity came at a price in terms of the level of security, which now is no more perfect but *statistical*: i.e. the construction is allowed to leak, but with negligible probability. To achieve this new definition, as we will explain in detail in the next subsection, they introduced the *average-case* security, formally defined as the *random probing model*. The average-case is in contraposition with the adversarial characteristic given so far, in which the adversary is restricted to t probes but of its own choice<sup>2</sup>. For obvious reasons, privacy that takes into consideration that kind of adversaries is referred to as *worst-case* security. On the other side, in the average-case, the attacker has no power over the leaking wires; instead, each wire of the circuit C will be considered probed with some independent probability p. Formally:

**Definition 3.6 (Random probing model [ISW03]).** A circuit transformer T = T(C, k) is said to be (statistically) p-private in the average case if C' = T(C, k) is statistically private against an adversary which corrupts each wire in C' with independent probability p. That is, the joint distribution of the random set of corrupted wires and the values observed by the adversary can be simulated up to a  $k^{-\omega(1)}$  statistical distance.

Consider now the ISW construction for the stateful model (see Theorem 3.5) with k number of shares. It should be easy to see that such a transformer is perfectly (k/4)-private. Using Chernoff's bound and a leakage probability  $p = \Omega(1/k)$  the authors claimed that every probe can be perfectly simulated but with negligible probability. This led them to state the following lemma:

**Lemma 3.7.** There exists a circuit transformer T(C, k) producing a circuit C' of size  $\mathcal{O}(|C| \cdot k^2)$ , such that T is  $\Omega(1/k)$ -private in the average case.

*Proof.* Let us first recall the Chernoff's bound. it is obtained by applying Markov's inequality to  $e^{tX}$ . For every t > 0:

<sup>&</sup>lt;sup>2</sup> Excluding the input wires in the stateless setting.

$$\Pr[X \ge a] = \Pr[e^X \ge e^a] \le \frac{\mathbb{E}[e^{t \cdot X}]}{e^{t \cdot a}}$$

Assume  $X = X_1 + \dots + X_n$  where  $X_1, \dots, X_n$  are independent variables. We get for any t > 0:

$$\Pr[X \ge a] \le e^{-t \cdot a} \prod_{i=1}^{n} \mathbb{E}[e^{tX_i}]$$

If the variables  $X_i$  have their value in  $\{0, 1\}$ , letting  $p_i = \Pr[X_i = 1]$ , we get:

$$\mathbb{E}[e^{tX_i}] = e^0 \cdot (1 - p_i) + e^t \cdot p_i = 1 + p_i \cdot (e^t - 1) \le e^{p_i \cdot (e^t - 1)}$$

This gives:

$$\Pr[X \ge a] \le e^{-t \cdot a} \cdot e^{\sum_{i=1}^{n} p_i \cdot (e^t - 1)} = e^{-t \cdot a + \mu \cdot (e^t - 1)}$$

where we let  $\mu = \mathbb{E}[X] = \sum_{i=1}^{n} p_i$ . We take  $a = (1 + \delta) \cdot \mu$  for  $\delta > 0$ . We take  $t = \log(1 + \delta)$ . This gives the Chernoff bound:

$$\Pr[X \ge (1+\delta)\mu] \le \left(\frac{e^{\delta}}{(1+\delta)^{1+\delta}}\right)^{\mu}$$

Using the inequality  $2\delta/(2+\delta) \leq \log(1+\delta)$ , we obtain:

$$\Pr[X \ge (1+\delta)\mu] \le \exp\left(\frac{-\delta^2\mu}{2+\delta}\right)$$

For  $\delta \geq 1$ , we have:

$$\Pr[X \ge (1+\delta)\mu] \le \exp\left(\frac{-\delta\mu}{3}\right)$$

Moreover, before getting into the proof itself, we would like to remark that such proof has been made explicit by us since it was just given as a statement in [ISW03]. Thus, let us consider the ISW construction from Theorem 3.3, i.e. the perfect private scheme in the stateless probing model, but with a number of shares dependent from the security parameter k, i.e. n = 2k + 1, and, consequently, secure against the probing of at most k probes per gadget, where each gadget has a number of wires  $m \leq c \cdot k^2$  for some constant c.

Hence, let  $X_1, \ldots, X_m$  be independent Bernoulli random variables, where  $X_i = 1$  if the *i*-th wire is probed, and  $X_i = 0$  otherwise; it holds that  $\Pr[X_i = 1] = p$  for all  $1 \le i \le m$ . Let  $X = X_1 + \ldots + X_m$  be the total number of leaking wires in the gadget. Theorem 3.3 guarantees that it is possible to perfectly simulate the probed wires if X does not exceed k. Thus, using the Chernoff bound with  $\delta \ge 1$  (see ??), it is possible to calculate the probability that the event X > k occurs:

$$\Pr[X \ge (1+\delta)\mathbb{E}[X]] \le \exp\left(-\frac{\delta}{3}\mathbb{E}[X]\right)$$

(3.1)

where  $\mathbb{E}[X]$  is computable and equal to  $p \cdot m$ . Furthermore, we fix  $p = 1/(2c \cdot k)$ . In addition, since we must upper-bound  $\Pr[X \ge k]$ , we can fix  $\delta$  such that:

$$k = (1+\delta)\mathbb{E}[X]$$

It is possible to explicate k from the number of wires  $m \leq c \cdot k^2$ ; this gives that:

$$1 + \delta = \frac{k}{\mathbb{E}[X]} = \frac{k}{p \cdot \ell} = \frac{2c \cdot k^2}{\ell} \ge \frac{2c \cdot k^2}{c \cdot k^2} \ge 2$$

and therefore the inequation  $\delta \geq 1$  is respected, as required. Moreover, it holds that:

$$\frac{\delta}{3}\mathbb{E}[X] = \frac{\delta}{3}\cdot \frac{k}{1+\delta} \geq \frac{k}{6}$$

Therefore, from (Equation (3.1)), it is possible to compute the probability:

$$\Pr[X \ge k] \le \exp(-k/6)$$

Hence, from the equation above, the simulation failure probability over all the gadgets is computed multiplying the failure probability of a single gadget for the total number of gadgets, i.e. it is at most  $|C| \cdot \exp(-k/6)$ .

For the sake of clarity, we stress the fact that this model is not able to provide worst-case security. The goal to guarantee privacy when the attacker can probe a  $\Omega(|C'|/k)$  of wires is still considered unachievable. As we are going to see in the next subsection, the relevance that Ishai et al. gave to the random probing model was to use it as a building block necessary to achieve statistical privacy in the worst-case setting.

#### 3.1.4 Statistical Privacy for Stateless Circuits

**Definition.** To obtain a construction with complexity  $\mathcal{O}(t \log t)$ , the authors introduced a relaxation to the security model, in which it is tolerated a leakage of the secrets, albeit with a negligible probability; this is called the statistical model of security. But the weaker privacy guarantees will be balanced by the  $\mathcal{O}(t \log t)$  complexity of the construction. However, to avoid confusion, let's remind the reader we are back to the worst-case scenario, where the adversary can choose the probes it wants up to t. Although the construction will make use of the average-case transformer, statistical privacy is defined to consider only attackers that can freely choose. The definition below is similar to the perfect privacy model, except that now the simulation can fail with negligible probability:

**Definition 3.8 (Statistical privacy for stateless circuits).** Let T be an efficiently computable deterministic function mapping a stateless circuit C to a stateless circuit  $\tilde{C}$ , and let

I, O be as above. We say that (T, I, O) is a statistically t-private stateless transformer if it satisfies the:

- 1. **Soundness.** The input-output functionality of  $O \circ \tilde{C} \circ I$  (i.e., the iterated application of  $I, \tilde{C}, O$  in that order) is indistinguishable from that of C.

- 2. **Privacy.** We require that the view of any t-limited adversary, which attacks  $O \circ \tilde{C} \circ I$  by probing at most t wires in  $\tilde{C}$ , can be simulated except with negligible probability. The identity of the probed wires has to be chosen in advance by the adversary.

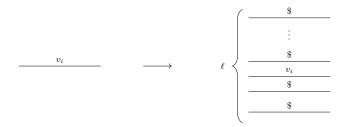

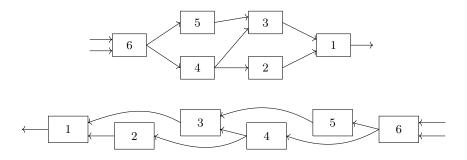

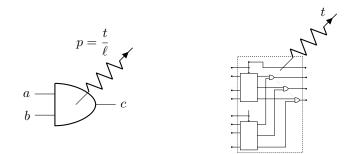

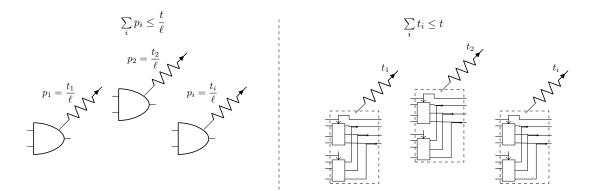

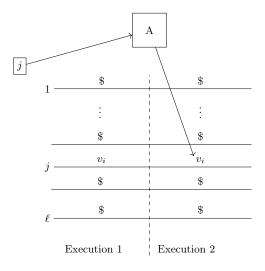

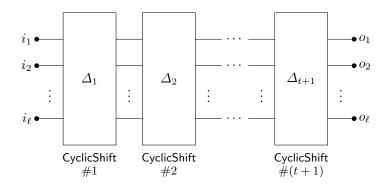

**Construction.** Their construction proceeds in two steps. Firstly, the masking countermeasure seen in Section 3.1.3 is applied; namely, the transformer T(C, k) proved to be *p*-private in the average-case, for  $p = \Omega(1/k)$  with security parameter *k*. Secondly, C' = T(C, k) is transformed into a larger circuit  $\widetilde{C}$ , where only a fraction of the computation is useful. In other words, the circuit  $\widetilde{C}$  would perform the same computation as C', but only on a small random subset of its wires; the remaining wires of  $\widetilde{C}$  would contain no useful information for the adversary. More specifically, the transformer  $\widetilde{T}$  mapping C' in  $\widetilde{C}$  takes each wire *i* of C' and replaces it with a new set of  $\ell$  wires in  $\widetilde{C}$ ; say each *i* is replaced by  $(i, 1), \ldots, (i, \ell)$ . Recall that every such wire can take a value from the set  $\{0, 1, \$\}$ . Thus, for every wire *i* in C' carrying a value  $v_i \in \{0, 1\}$ , the wires  $(i, 1), \ldots, (i, \ell)$  in  $\widetilde{C}$  carry the value  $v_i$  in a random position (independently of other  $\ell$ -tuples), and the value \$ in the all remaining  $\ell-1$  ones; see Figure Figure 31 for an illustration.

Fig. 31: A wire with signal  $v_i$  in C' (left), and the corresponding  $\ell$  wires in  $\widetilde{C}$  (right); only one of the  $\ell$  wires contains the signal  $v_i$ , while the others contain the dummy value \$.

Consequently to the above rearrangements of wires, modifications to the encoding and decoding are required. The old algorithms no longer fit the expanded circuit logic; nevertheless, from the implementation point of view, the new Encode' and Decode' use the old Encode and Decode as a subroutine. But now, for the sake of simplicity, the following descriptions will not take into account this last remark:

Encode'. To encode a value v, first generate at random an index j

<sup>\$</sup> [1, ℓ] and output an ℓ-tuple in which v will be the j-th element, while the other elements carry a dummy value \$. That is, return (\$,...,\$, v, \$,...,\$), where v is at the j-th position.

• Decode'. Given a  $\ell$ -tuple  $(\$, \ldots, \$, v, \$, \ldots, \$)$ , return v.

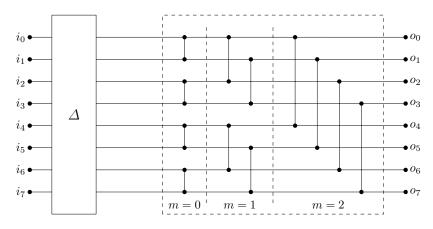

Once the encoding and decoding algorithms are adjusted, let's pass to the transformation of the intermediate circuit. Hence, consider a gate in C' such that input wires  $i_1$  and  $i_2$  are processed to obtain  $v_i = v_{i_1} * v_{i_2}$ ; namely, the *i*-th wire of C' is computed by applying a boolean operation  $* \in \{AND, XOR\}$  to the  $i_1$ -th and the  $i_2$ -th wire of C'. Informally,  $\tilde{T}$  would transform such gate in a  $2\ell$ -input,  $\ell$ -output gadget in  $\tilde{C}$ . The gadget, first, puts both values  $v_{i_1}$  and  $v_{i_2}$  in random but adjacent positions, and then it combines them to obtain the value  $v_{i_1} * v_{i_2}$  in a randomly defined wire out of the  $\ell$  output ones. In order to achieve the "random but adjacent position" property, the construction resorted to a *sorting network* as a building block, see [AKS83]. Technically, the gate processing is described in [ISW03] as follows:

- **Preprocessing.** Compute  $\ell + 1$  uniformly and independently random integers  $r, r_1, \ldots, r_\ell$  from the range  $[0, 2^k]$ , where k is the security parameter. For each  $1 \le j \le \ell$ , use the values  $v_{i_1,j}, v_{i_2,j}$  (of wires  $(i_1, j)$  and  $(i_2, j)$ ) to form a pair (key<sub>i</sub>, val<sub>j</sub>) such that:

- 1. key<sub>i</sub> is set to  $r_j$  if  $v_{i_1,j} = v_{i_2,j} =$ \$ and to r otherwise;

- 2.  $\operatorname{val}_j$  is set to \$ if both  $v_{i_1,j}$ ,  $v_{i_2,j}$  are \$; to a bit value b if one of  $v_{i_1,j}, v_{i_2,j}$  is b and the other is \$, and to  $b_1 * b_2$  if  $v_{i_1,j} = b_1$  and  $v_{i_2,j} = b_2$ .

- Sorting. A sorting network is applied to the above ℓ-tuple of pairs using key as the sorting key. Let (u<sub>1</sub>,..., u<sub>ℓ</sub>) denote the ℓ-tuple of symbols val<sub>j</sub> sorted according to the keys key<sub>j</sub>.

- **Postprocessing.** The *j*-th output  $v_j$  is obtained by looking at  $u_j$ ,  $u_{j+1}$ ,  $u_{j+2}$ : if  $u_j$ ,  $u_{j+1} \neq \$$  then  $v_j = u_j * u_{j+1}$ , if  $u_j = u_{j+2} = \$$  and  $u_{j+1} \neq \$$  then  $v_j = u_{j+1}$ , and otherwise  $v_j = \$$ .