PhD-FSTC-2015-57

The Faculty of Sciences, Technology and Communication

## DISSERTATION

Defense held on 24/11/2015 in Luxembourg

to obtain the degree of

# DOCTEUR DE L'UNIVERSITÉ DU LUXEMBOURG EN PHYSIQUE

by

**Thomas Paul WEISS**

Born on 1<sup>st</sup> of March 1986 in Bad Kreuznach, (Germany)

## ELECTRICAL CHARACTERIZATION OF KESTERITE THIN FILM ABSORBERS AND SOLAR CELLS

### Dissertation defense committee

Dr Susanne Siebentritt, dissertation supervisor

*Professor, Université du Luxembourg*

Dr Alex Redinger

*Helmholtz-Zentrum Berlin für Materialien und Energie*

Dr Michels Andreas, Chairman

*Professor, Université du Luxembourg*

Dr Uwe Rau

*Professor, Forschungszentrum Jülich – Institut für Energie und Klimaforschung*

Dr Schmidt Thomas, Vice Chairman

*Professor, Université du Luxembourg*

# CONTENTS

|                                                       |           |

|-------------------------------------------------------|-----------|

| <b>1. Introduction</b>                                | <b>7</b>  |

| 1.1. Defect characterization . . . . .                | 8         |

| 1.2. Overview of this thesis . . . . .                | 10        |

| <b>2. Fundamentals of solar cell devices</b>          | <b>13</b> |

| 2.1. n+p heterojunction . . . . .                     | 13        |

| 2.2. CZTSe solar cells . . . . .                      | 15        |

| 2.2.1. Solar cell structure . . . . .                 | 15        |

| 2.2.2. Bandalignment . . . . .                        | 17        |

| 2.3. IV analysis . . . . .                            | 18        |

| 2.3.1. Recombination processes . . . . .              | 19        |

| 2.3.2. Shockley-Read-Hall recombination . . . . .     | 20        |

| 2.3.3. Solar cell parameters . . . . .                | 21        |

| <b>3. Growth of the CZTSe absorber layer</b>          | <b>25</b> |

| 3.1. PVD system . . . . .                             | 25        |

| 3.2. Sequential process . . . . .                     | 26        |

| 3.2.1. Decomposition reaction . . . . .               | 26        |

| 3.2.2. Precursor growth at 320 °C . . . . .           | 27        |

| 3.2.3. Precursor growth at low temperatures . . . . . | 27        |

| 3.2.4. High temperature annealing . . . . .           | 28        |

| 3.3. High temperature co-evaporation . . . . .        | 30        |

| 3.3.1. Overview of literature processes . . . . .     | 31        |

| 3.3.2. Our process . . . . .                          | 31        |

| 3.3.3. Additional heat treatment . . . . .            | 33        |

| 3.4. CdS thickness variation . . . . .                | 34        |

| 3.4.1. Absorber growth . . . . .                      | 34        |

| 3.4.2. CdS growth . . . . .                           | 34        |

| 3.5. Differences in microstructure . . . . .          | 36        |

| <b>4. Experimental setup</b>                          | <b>39</b> |

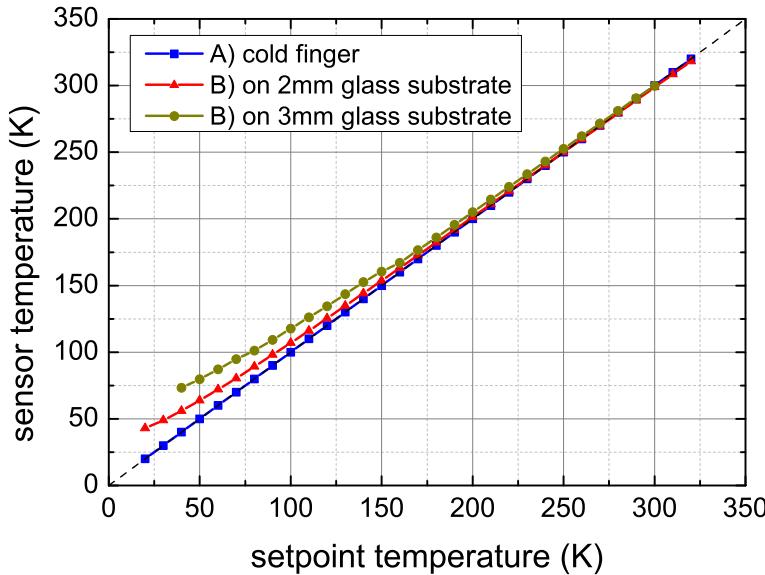

| 4.1. Temperature control . . . . .                    | 40        |

| 4.2. Capacitance measurements . . . . .               | 41        |

| 4.3. IVT measurements . . . . .                       | 42        |

## Contents

|                                                                                    |            |

|------------------------------------------------------------------------------------|------------|

| 4.4. IV measurements . . . . .                                                     | 42         |

| <b>5. Characterization by capacitance measurements</b>                             | <b>43</b>  |

| 5.1. Capacitance voltage measurements . . . . .                                    | 44         |

| 5.1.1. Determination of $V_{bi}$ and $N_A$ . . . . .                               | 45         |

| 5.1.2. Influence of deep defects on the built-in voltage . . . . .                 | 46         |

| 5.2. Admittance spectroscopy . . . . .                                             | 47         |

| 5.2.1. Calculation of trap energy . . . . .                                        | 51         |

| 5.3. Defect distributions . . . . .                                                | 52         |

| 5.3.1. Walter analysis . . . . .                                                   | 53         |

| 5.3.2. Fitting of the capacitance spectrum . . . . .                               | 55         |

| 5.3.3. Comparison of evaluation methods . . . . .                                  | 60         |

| 5.4. Alternative origins for capacitance steps . . . . .                           | 61         |

| 5.4.1. Influence of the series resistance . . . . .                                | 61         |

| 5.4.2. Carrier freeze-out . . . . .                                                | 63         |

| 5.4.3. Back contact barrier . . . . .                                              | 64         |

| 5.4.4. Inversion layer or interface defects . . . . .                              | 65         |

| 5.4.5. Mobility freeze-out . . . . .                                               | 67         |

| 5.5. On sequentially processed absorbers . . . . .                                 | 69         |

| 5.5.1. Capacitance voltage curves . . . . .                                        | 69         |

| 5.5.2. Admittance . . . . .                                                        | 72         |

| 5.6. On co-evaporated absorbers . . . . .                                          | 81         |

| 5.6.1. As grown absorber layers . . . . .                                          | 81         |

| 5.6.2. Impact of annealing after co-evaporation . . . . .                          | 83         |

| 5.7. Interpretation of the low temperature capacitance transition . . . . .        | 87         |

| 5.7.1. Mobility freeze-out . . . . .                                               | 87         |

| 5.7.2. CdS thickness variation . . . . .                                           | 88         |

| 5.8. Summary . . . . .                                                             | 90         |

| <b>6. Characterization of solar cells by temperature dependent IV measurements</b> | <b>93</b>  |

| 6.1. Temperature dependent IV analysis . . . . .                                   | 93         |

| 6.1.1. Dominant recombination pathway . . . . .                                    | 93         |

| 6.1.2. Series resistance . . . . .                                                 | 94         |

| 6.2. On sequentially processed absorbers . . . . .                                 | 99         |

| 6.2.1. Loss of forward diode current . . . . .                                     | 100        |

| 6.2.2. Loss of photo current . . . . .                                             | 103        |

| 6.2.3. Dominant recombination pathway . . . . .                                    | 104        |

| 6.3. On co-evaporated absorbers . . . . .                                          | 105        |

| 6.3.1. As grown . . . . .                                                          | 105        |

| 6.3.2. Additional heat treatment . . . . .                                         | 108        |

| 6.4. Summary and interpretation of IVT measurements . . . . .                      | 110        |

| 6.4.1. Dominant recombination pathway . . . . .                                    | 111        |

| 6.4.2. Series resistance and drop of photo current . . . . .                       | 112        |

| <b>7. Model for current CZTSe devices</b>                                          | <b>115</b> |

| 7.1. Overview of device characteristics . . . . .                                  | 115        |

| 7.2. Analysis of capacitance spectra with the fitting routine . . . . .            | 117        |

|                     |                                                                                    |            |

|---------------------|------------------------------------------------------------------------------------|------------|

| 7.3.                | Low temperature behaviour . . . . .                                                | 117        |

| 7.3.1.              | Series resistance and final capacitance step . . . . .                             | 117        |

| 7.3.2.              | Second capacitance step . . . . .                                                  | 118        |

| 7.4.                | High temperature capacitance transition and open circuit voltage deficit . . . . . | 119        |

| <b>8.</b>           | <b>Acknowledgments</b>                                                             | <b>121</b> |

| <b>A.</b>           | <b>Sites method</b>                                                                | <b>123</b> |

| A.1.                | Influence of shunt resistance . . . . .                                            | 123        |

| A.2.                | Implementation and analysis . . . . .                                              | 124        |

| <b>B.</b>           | <b>Collection function</b>                                                         | <b>126</b> |

| <b>C.</b>           | <b>IVT measurements</b>                                                            | <b>128</b> |

| C.1.                | $V_{oc}$ extrapolation . . . . .                                                   | 128        |

| C.2.                | QE of sample from $V_{oc}$ extrapolation analysis . . . . .                        | 131        |

| C.3.                | Evaluation of dark IV curves of as-grown co-evaporated samples . . . . .           | 132        |

| <b>D.</b>           | <b>Additional graphs of capacitance measurements</b>                               | <b>133</b> |

| D.1.                | CV of as-grown high temperature co-evaporated samples . . . . .                    | 133        |

| D.2.                | Capacitance derivative after heat treatment . . . . .                              | 133        |

| <b>E.</b>           | <b>CdS thickness variation</b>                                                     | <b>135</b> |

| E.1.                | Device characteristics . . . . .                                                   | 135        |

| E.2.                | Fitted capacitance spectra for CdS thickness series . . . . .                      | 137        |

| <b>F.</b>           | <b>Publications and conference contributions</b>                                   | <b>140</b> |

| <b>Bibliography</b> |                                                                                    | <b>147</b> |

---

CHAPTER

**ONE**

---

## INTRODUCTION

Thin film solar cells have great perspective in terms of a competitive sustainable energy source [1]. In the lab CdTe and Cu(In,Ga)Se<sub>2</sub> (CIGSe) have already achieved record device efficiencies of 21.5% [2] and 21.7% [3], respectively. However, for installations in the TW scale a concern of these technologies is the scarcity of In and Te [1], which requires looking for new materials.

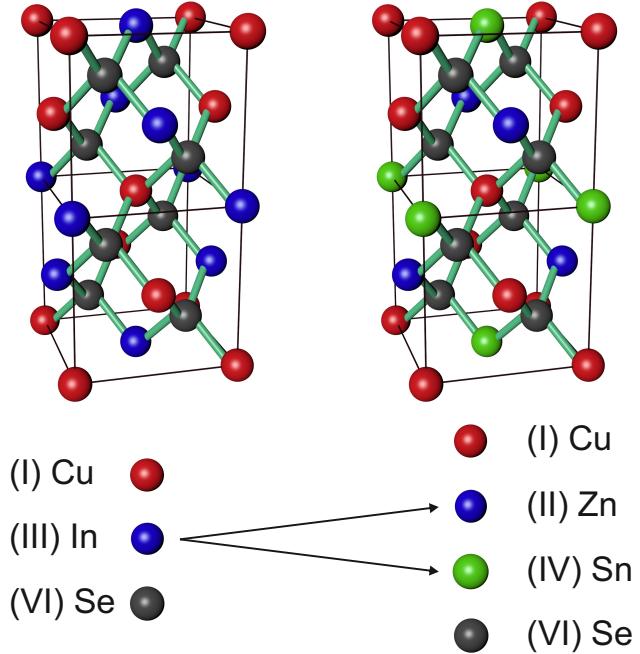

One promising candidate is the material system Cu, Zn, Sn, S(e). It crystallizes in the kesterite structure [4], which can be derived from the chalcopyrite structure as shown in Fig. (1.1) [5]. Starting from Cu(In,Ga)Se<sub>2</sub>, the group three element In/Ga is replaced by the group two and group four element Zn and Sn, respectively such that it forms Cu<sub>2</sub>ZnSnSe<sub>4</sub> (CZTSe). Alloying with S results in Cu<sub>2</sub>ZnSn(S,Se)<sub>4</sub> (CZTSSe) and allows for engineering the bandgap between 1.0 eV and 1.5 eV for Cu<sub>2</sub>ZnSnSe<sub>4</sub> and Cu<sub>2</sub>ZnSnS<sub>4</sub>, respectively [6]. Experimentally and theoretically, a direct bandgap was found for these semiconductors [7] and therefore the interesting range of bandgaps for solar cell applications [8] can be covered.

Due to the similarity with CIGSe, the same solar cell structure can be used, which is a soda lime glass (SLG)/Mo substrate and a CdS/i:ZnO/Al:ZnO window layer [9]. The highest efficiency so far was demonstrated for a mixed S and Se device, i.e. Cu<sub>2</sub>ZnSn(S,Se)<sub>4</sub> (CZTSSe), with a power conversion efficiency of 12.6% [10]. The highest efficiency for the pure Se and S devices reached values of 11.6% [11] and 9.2% [12], respectively. Note that the 9.2 CZTS device was fabricated with an CdS/In<sub>2</sub>S<sub>3</sub> buffer layer. A recent review paper by Fella *et al.* [13] summarizes the different growth techniques employed for reaching high efficient kesterite devices. In contrast to CIGSe, the highest efficiencies for CZTSSe are reached by non-vacuum deposition techniques with a sequential process [10]. The best high temperature co-evaporated device is made by NREL with 9.4% [14].

The major problem in achieving higher efficiencies is a high open circuit voltage deficit for all kesterite based devices [15]. Repins *et al.* [14] observed for high efficient (9.4%) co-evaporated CZTSe devices lifetimes around 2 - 3 ns, which is small compared to lifetimes above 100 ns observed for high efficient CIGSe devices [16]. However, the authors also pointed out that these small lifetimes responsible for the low observed open circuit voltages cannot alone be due to deep Shockley-Read-Hall (SRH) recombination centres. Gokmen *et al.* [17] pointed out that also strong tailing occurs in CZTSe devices, which could explain the low  $V_{oc}$  values for the low bandgap CZTSSe (high [Se]/([Se] + [S]) ratio) devices. However, for higher S contents the tailing alone is not sufficient to describe the  $V_{oc}$  deficit and therefore also other effects need to be taken into account. In Ref. [17] it was also proposed that the tailing could be due to

## 1. Introduction

**Figure 1.1.: Comparison of chalcopyrite and kesterite crystal structure** - Crystal structure of kesterite is obtained if In with 3 outer electrons is replaced by Zn and Sn with 2 and 4 outer electrons, respectively. Image adapted from Ref. [5].

electrostatic potential fluctuations due to the  $[\text{Cu}_{\text{Zn}} + \text{Zn}_{\text{Cu}}]$  antisite defect complex. Indeed, due to the low formation energy of 0.21 eV for this defect [18] a large number of these defects is expected at room temperature [17]. A high Urbach energy was also observed by Redinger *et al.* [19]. Experimentally, a phase transition between the ordered and disordered kesterite was observed [4, 20–22], where the disordered kesterite is characterized by a random site occupation by Cu and Zn atoms in the Cu-Zn planes (see Fig. (1.1)). The critical temperatures are found to be 260 °C and 200 °C for the pure S [20] and pure Se [22] kesterite. Below these temperatures, the degree of ordering increases with lowering temperatures, but will reach the perfectly ordered state only at 0 K, i.e. there will be always  $[\text{Cu}_{\text{Zn}} + \text{Zn}_{\text{Cu}}]$  antisite defect states present at operating temperatures [22].

### 1.1. Defect characterization

All these points discussed above (small minority carrier life times, tailing) lead to the desire of a better understanding of the defects present in the kesterite samples to gather a better understanding of the low  $V_{oc}$ . One commonly applied technique for defect characterization is thermal admittance spectroscopy developed by Losee [23]. Measuring the capacitance (and conductance) with respect to frequency and/or temperature enables the detection of possible defect states in the sense that a drop in capacitance is observed from low to high frequencies and high to low temperatures. Walter *et al.* [24] refined this theory such that it is possible to extract defect distributions from an admittance spectrum. For the compound CIGSe for instance Hanna *et al.* [25] could show with the help of admittance spectroscopy that the concentration

### 1.1. Defect characterization

of a specified defect correlates with the open circuit voltage deficit and that the lowest defect concentration is obtained for a  $[Ga]/([Ga] + [In])$  of 0.3, which is the value where the best CIGSe devices are prepared (without potassium treatment) [26]. For CZTSe I could show that a deep defect distribution is introduced after annealing appearing as a broad high temperature capacitance transition with a detrimental effect on the  $V_{oc}$  [27].

In literature only a few papers are published dealing with admittance spectroscopy on kesterite based solar cells. Additionally, these papers discuss solely the commonly observed low temperature capacitance transition. A summary of these papers is given in Tab. 1.1. The first row indicates the material of the absorber, i.e. whether the measurements were done on pure S, pure Se or SSe devices.

The second row reports the appearance of the major capacitance transition. The major capacitance transition is characterized by exhibiting clearly identifiable inflection frequencies in the observed temperature range. Some groups find that this capacitance transition results from a single step, while others find this transition to be composed of two (generally overlapping) capacitance steps. Evidently, the appearance of this transition is not linked to the  $[Se]/([Se] + [S])$  ratio. However, in almost all publications the high frequency and low temperature capacitance seems to be the geometrical capacitance. Despite that fact the observed capacitance step(s) are nevertheless often attributed (and also evaluated) as deep defects. Clearly, a better picture of the low temperature behaviour in admittance spectroscopy needs to be settled.

The third row indicates whether the above mentioned high temperature capacitance transition is observed. Interestingly, many groups also observe such a transition but no further investigations were carried out. Even the 10.1 % efficient CZTSSe device reported in Ref. [28] shows a strong rise of capacitance with lowered frequencies and increased temperatures pointing to the fact that also in these high efficient hydrazine processed absorbers the detrimental deep defect distribution is present.

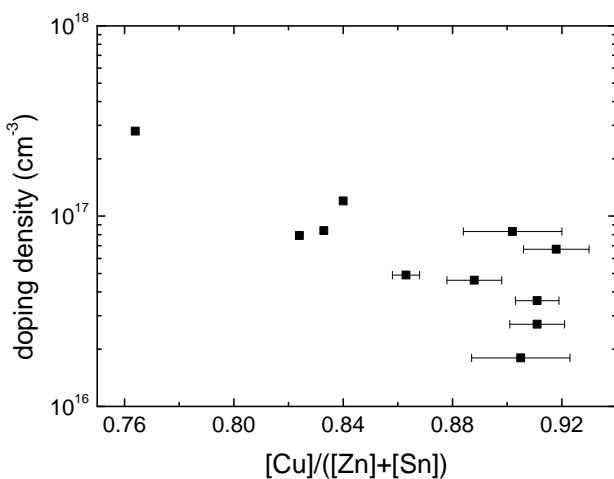

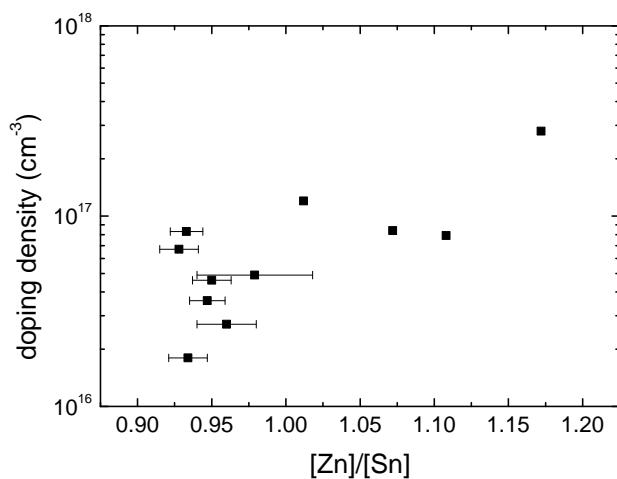

Some groups also investigate the doping density either by capacitance-voltage (CV) profiling [29] or by drive-level capacitance profiling (DLCP) [30]. The deduced values are given in rows 4 and 5 in Tab. 1.1. The list for the reported values of doping densities is not complete. Many other groups also measured the doping density (by CV or DLCP) but not an admittance spectrum. These papers are therefore omitted in Tab. 1.1. However, while theoretically the  $Zn_{Cu}$  antisite defect is predicted to be the dominant doping acceptor [18], experimentally no conclusive picture can be drawn.

Within the scope of this thesis I have characterized CZTSe based solar cells with the help of admittance spectroscopy and CV measurements. Based on these measurements I will show that the high temperature capacitance transition is due to a broad deep defect distribution which has a detrimental effect on the  $V_{oc}$ . This finding is presented in section 5.5.2.2 and was also published in Ref. [27]. Thus, if this deep defect can be prevented by finding suitable annealing conditions, it would help to lower the above mentioned high  $V_{oc}$  deficit in kesterite based solar cells.

Concerning the major capacitance transition, I generally observed an overlapping double capacitance step for CZTSe devices as I have demonstrated in Ref. [27, 41, 43]. I will show that these steps occur below the space charge region (SCR) capacitance and therefore cannot be attributed to deep defect levels. In literature, the final capacitance step was interpreted as a carrier freeze-out [31]. However, in section 5.7 I will show that a mobility freeze-out is also a reasonable explanation. For the origin of the second capacitance step I suggest a barrier due to the buffer layer. This assumption is backed up by temperature dependent IV measurements.

## 1. Introduction

**Table 1.1.:** List of publications dealing with admittance spectroscopy on kesterite based solar cells.

| absorber       | low temp.<br>transition  | high temp.<br>transition | doping density                      | method | Ref. |

|----------------|--------------------------|--------------------------|-------------------------------------|--------|------|

| CZTSSe         | single step              | yes                      | $8 \cdot 10^{15}$                   | DLCP   | [28] |

| CZTSSe - CZTS  | single step              | no                       | $1 \cdot 10^{15} - 1 \cdot 10^{16}$ | DLCP   | [31] |

| CZTSSe         | single step              | yes                      | N/A                                 | -      | [32] |

| CZTSSe - CZTS  | single step              | yes, small               | $1 \cdot 10^{15} - 1 \cdot 10^{16}$ | DLCP   | [33] |

| CZTSe          | single step              | no                       | $1 \cdot 10^{15}$                   | CV     | [34] |

| CZTS           | single step              | no                       | N/A                                 | -      | [35] |

| CZTS           | double step              | N/A                      | N/A                                 | -      | [36] |

| CZTSSe         | double step              | yes, small               | $1 \cdot 10^{16} - 1 \cdot 10^{17}$ | CV     | [37] |

| CZTSSe - CZTS  | double step <sup>a</sup> | no                       | N/A                                 | -      | [38] |

| CZTS           | double step              | yes                      | N/A                                 | -      | [39] |

| CZTSe - CZTSSe | double step              | yes                      | N/A                                 | -      | [40] |

| CZTSe          | double step              | yes                      | $1 \cdot 10^{15} - 1 \cdot 10^{17}$ | CV     | [41] |

| CZTSe          | double step              | (yes) <sup>b</sup>       | $2 \cdot 10^{16}$                   | CV     | [42] |

<sup>a</sup> only one step (the higher energetic one) is discussed.

<sup>b</sup> capacitance spectra are not shown. But a deep defect around midgap was found by DLTS.

To be able to quantify the overlapping double capacitance step I will present a new evaluation method capable of fitting the complete temperature dependent capacitance spectrum (section 5.3.2). With that approach the double capacitance step is deconvoluted, which is not possible with the Walter method [24]. Additionally, this method allows the characterization of the afore mentioned high temperature capacitance transition which lead to the assignment to a detrimental deep defect distribution.

## 1.2. Overview of this thesis

I will start the thesis with a discussion of solar cell devices in chapter 2. It includes the theoretical description of a  $n^+p$  junction (section 2.1) followed by the actual solar cell structure used for CZTSe absorber layers (section 2.2). The last section 2.3 deals with the description and analysis of current-voltage (IV) curves. It discusses different recombination processes and how the parameters describing the IV curve can be extracted from experiment.

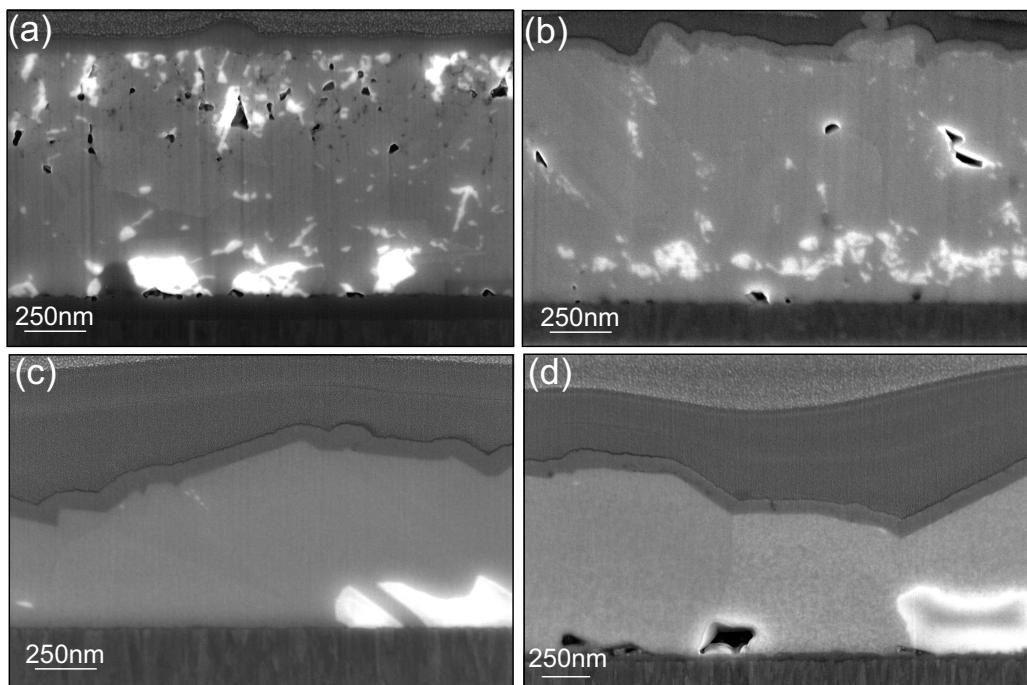

Chapter 3 describes the growth of CZTSe absorber layers. It first explains the PVD growth chamber (section 3.1), in which the precursor and absorber layers are grown. I have applied two different approaches for the growth of absorber layers: a sequential (section 3.2) and a high temperature co-evaporation process (section 3.3). The difference in the microstructure resulting from these growth processes was investigated by scanning electron microscopy (SEM) and is presented in section 3.5.

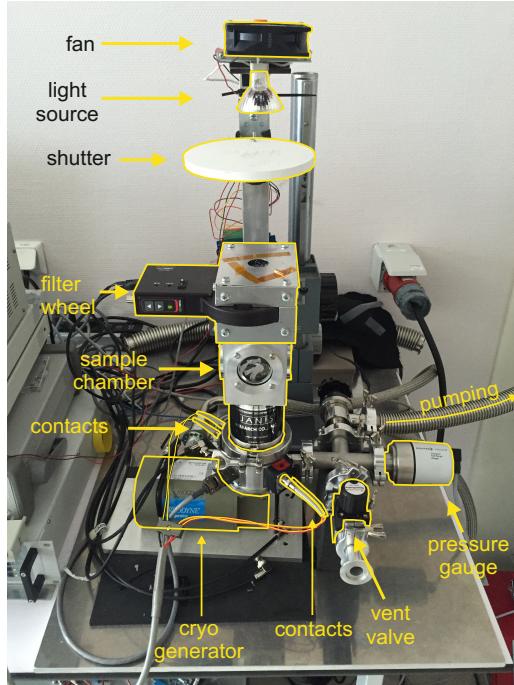

The experimental setup for IV, IVT and admittance measurements is presented in chapter 4.

Chapter 5 is dedicated to the characterization by capacitance measurements. It covers the theoretical background of CV and admittance measurements in sections 5.1 to 5.4. Sections 5.5 and 5.6 will then cover the experimental results for the sequentially processed and co-evaporated samples, respectively. A discussion on the interpretation of the major capacitance step seen by

## 1.2. Overview of this thesis

admittance spectroscopy will be given in section 5.7. Section 5.8 summarizes the findings and information obtained from the capacitance measurements.

Chapter 6 deals with the characterization by temperature dependent IV measurements. The chapter introduces first the theoretical background in section 6.1. It covers the evaluation of the dominant recombination pathway and discusses possible mechanisms which lead to a thermally activated series resistance as it is observed experimentally. Section 6.2 and section 6.3 then discuss the results for the sequentially processed and co-evaporated samples, respectively. The interpretation of these results is then discussed and summarized in section 6.4.

In chapter 7 a common model is put up which describes the experimentally features from IVT and capacitance measurements.

---

CHAPTER

**TWO**

---

## FUNDAMENTALS OF SOLAR CELL DEVICES

A solar cell is a semiconductor device and based on a pn junction. If the n-type semiconductor is much higher doped than the p-type semiconductor such a junction is called a  $n^+p$  junction. Such an asymmetric junction is the basis of thin film solar cells and will be discussed in section (2.1). For the thin film solar cells discussed in this work, the p-type semiconductor is the p-type CZTSe absorber layer and the Al:ZnO window layer is the  $n^+$  side. However, the exact structure of a whole solar cell device includes more layers and it will be discussed together with its band alignment in section (2.2).

Finally, the current-voltage characteristics of a solar cell will be discussed in section (2.3). It includes the discussion of different recombination pathways and their impact on an IV curve.

### 2.1. n+p heterojunction

A np junction is the connection of a n-type and a p-type semiconductor. If the same material is used for the n-type and p-type semiconductor, the junction is said to be a homojunction, while the connection of two semiconductors of different materials is called a heterojunction.

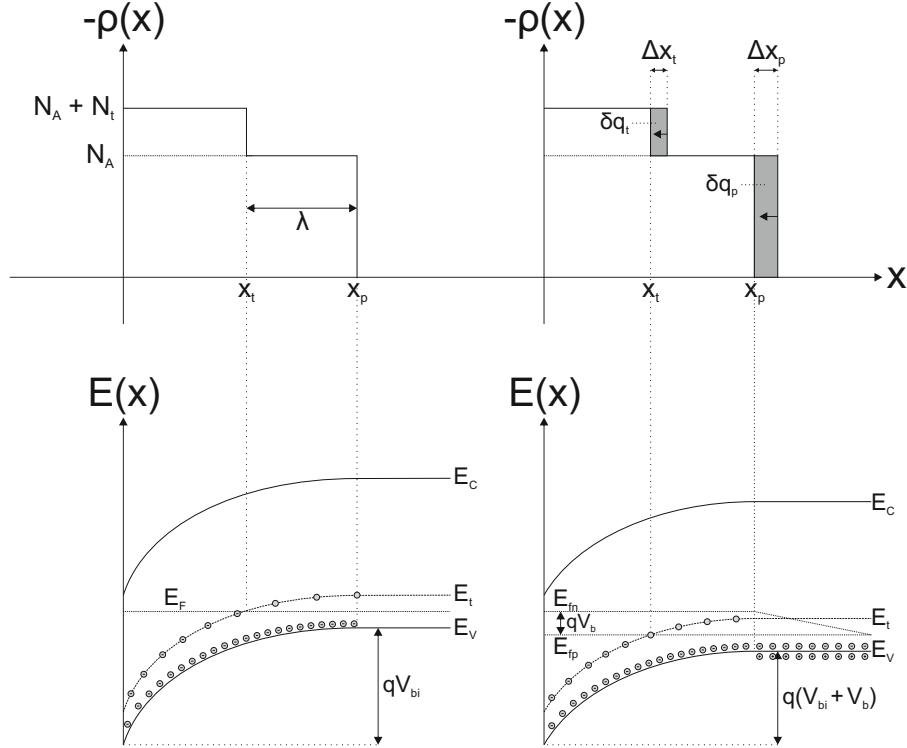

In the following I will quickly sketch the derivation of the space charge distribution, which in turn will result in formulas for the SCR width and the built-in voltage. These quantities will later be needed to discuss capacitance-voltage measurements (see section 5.1). Detailed derivations can be found in more detail in common textbooks for example in Ref. [44].

Bringing the p- and n-type semiconductor in contact, electrons from the n-side flow into the p-side and holes from the p- to the n-side. As a consequence, positive and negative charged ions form on the n-side and the p-side, respectively and therefore an electrostatic field is built up. In thermal equilibrium the forces due to a gradient of the chemical potential and a gradient of the electric potential cancel out such that the gradient of the electrostatic potential  $E_F$  equals zero and no electron (or hole) current flows, that is:

$$J_i = \mu_i i \frac{dE_F}{dx} = 0, \quad (2.1)$$

where  $i$  is either  $n$  or  $p$  for electrons or holes, respectively. It needs to be pointed out that the total current  $J_i$  equals zero because the forces cancel out and not due to two currents, the diffusion and the drift current, with equal magnitude but different signs. [45].

## 2. Fundamentals of solar cell devices

Thus, with the condition of a flat Fermi level across the pn-junction in thermal equilibrium, the built-in voltage  $V_{bi}$  is given by

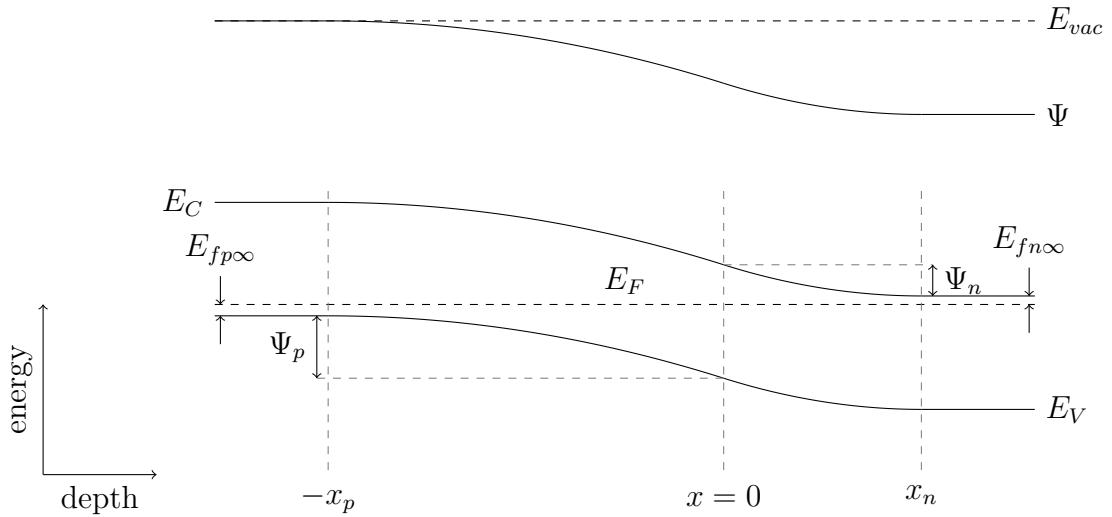

$$qV_{bi} = E_g - (qE_{fn\infty} + qE_{fp\infty}) = q\Psi_n + q\Psi_p, \quad (2.2)$$

where  $E_{fn\infty}$  ( $E_{fp\infty}$ ) denote the distance of the Fermi level from the conduction (valence) band of the n-type (p-type) semiconductor away from the junction and  $\Psi_n$  and  $\Psi_p$  the potential drop on the n- and p-side, respectively. A schematic of the notations of these values is shown in Fig. (2.1) for a pn homo junction. Therefore, with a higher doping density and thus a lower value of  $E_{fn\infty}/fp\infty$ , a higher  $V_{bi}$  is achieved.

**Figure 2.1.: Banddiagram of a pn homojunction** - Banddiagram is depicted in correct scale for a doping density of  $N_A = 5 \cdot 10^{15} \text{ cm}^{-3}$  and  $N_D = 1 \cdot 10^{16} \text{ cm}^{-3}$ . Since  $N_A < N_D$ , the SCR extends further into the bulk of the p-type semiconductor compared to the n-type semiconductor.

In order to calculate the SCR width we assume complete ionization of the dopants on each side, charge neutrality over the whole junction and an abrupt junction at  $x = 0$ . Additionally, we assume a box like charge distribution namely the depletion approximation. It assumes a space charge (per unit volume) of  $-N_A$  extending until  $x_p$  on the p-side and a space charge of  $N_D$  until  $-x_n$  on the n-side. Consequently, the charge neutrality reads:

$$N_A x_p = N_D x_n. \quad (2.3)$$

The SCR width is then obtained with the help of the Poisson equation, which links the electrostatic potential  $\Psi$  with the charge density  $\rho$  and reads

$$-\frac{d^2\Psi}{dx^2} = \frac{d\mathcal{E}}{dx} = \frac{q}{\epsilon_R \epsilon_0} \rho(x) \quad (2.4)$$

with

$$\rho(x) = \begin{cases} -N_D & : -x_n \leq x \leq 0 \\ N_A & : 0 < x \leq x_p \end{cases} \quad (2.5)$$

$\mathcal{E}$  denotes the electric field,  $\epsilon_R$  the dielectric constant of the material and  $\epsilon_0$  the vacuum permit-

tivity. By integrating Eqn. (2.4) the electric field across the SCR is obtained. At the transition from the p- to n-type semiconductor the electric field reaches its maximum  $\mathcal{E}_m$  and reads

$$\mathcal{E}_m = \frac{qN_D x_n}{\epsilon_R \epsilon_0} = \frac{qN_A x_p}{\epsilon_R \epsilon_0}, \quad (2.6)$$

assuming the same  $\epsilon_R$  for the p- and n-type semiconductor. Integrating Eqn. (2.4) a second time, the potential drops  $\Psi_p$  and  $\Psi_n$  on the p- and n-side respectively are obtained as

$$\Psi_p = \frac{qN_A x_p^2}{2\epsilon_R \epsilon_0} \quad \text{and} \quad \Psi_n = \frac{qN_D x_n^2}{2\epsilon_R \epsilon_0}. \quad (2.7)$$

Now, using Eqn. (2.2), (2.3), (2.6) and (2.7) the widths of the space charge regions are obtained with respect to the built-in voltage and the doping densities. For the p-side this is:

$$x_p = \sqrt{\frac{2\epsilon_R \epsilon_0 \Psi_{bi}}{q} \frac{N_D}{N_A(N_A + N_D)}} \quad (2.8)$$

and for the n-side:

$$x_n = \sqrt{\frac{2\epsilon_R \epsilon_0 \Psi_{bi}}{q} \frac{N_A}{N_D(N_A + N_D)}}. \quad (2.9)$$

Now, we assume  $N_D \gg N_A$  as in a n<sup>+</sup>p junction and Eqn. (2.8) and (2.9) simplify to

$$x_p \approx \sqrt{\frac{2\epsilon_R \epsilon_0 \Psi_{bi}}{qN_A}} \quad \text{and} \quad x_n \approx 0. \quad (2.10)$$

Thus, the SCR width only extends into the p-side and also the potential drops only on the p-side. For our structure the n<sup>+</sup>-layer will be the highly doped window layer in general Al:ZnO and the p-layer the CZTSe absorber layer. Therefore, for many considerations the n<sup>+</sup>p junction will be approximated as a Schottky contact as for example for admittance spectroscopy (see section 5.2. However, the structure of a whole solar cell device does not only consist of these two layers and will be discussed in section 2.2.

## 2.2. CZTSe solar cells

In the preceding section we discussed the simple case of a n<sup>+</sup>p junction. However, in reality the structure of a solar cell is more complex and with it its bandalignment. These two topics will be discussed in the following two sections.

### 2.2.1. Solar cell structure

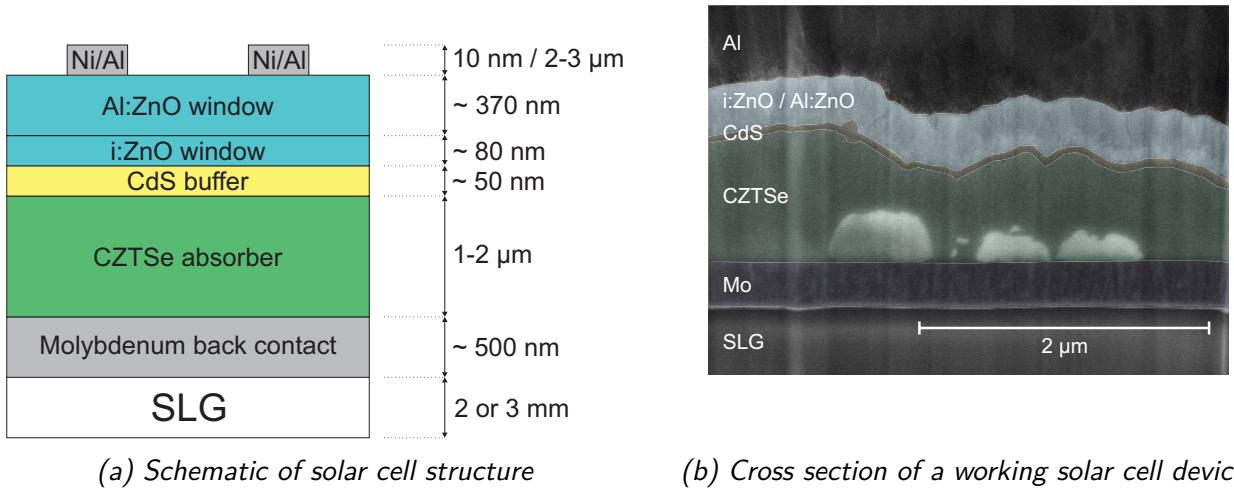

The schematic cross section of a CZTSe based solar cell is show in Fig. (2.2a).

The solar cell is in substrate configuration meaning that the absorber is grown on a metallic back contact and the light enters through a transparent conducting oxide (TCO), which represents the front contact.

The back contact consists of a roughly 400 nm sputtered Mo layer. On top of the Mo back contact the absorber or precursor layer is grown by co-evaporation, see sections (3.3) and

## 2. Fundamentals of solar cell devices

**Figure 2.2.: A thin film solar cell device** - CZTSe based solar cell device in substrate configuration shown as a schematic (a) and of a real device (b). The Ni layer of the grid is too thin to be resolved and the difference between Al:ZnO and i:ZnO is only hardly visible. The cross section in (b) was prepared by a focused ion beam (FIB) from the device with a double CdS buffer layer (c.f. section 3.4).

(3.2) for details on the absorber growth processes. The absorber layer represents the p-type semiconductor as discussed in section 2.1.

Between the n<sup>+</sup> window layer and the p-type absorber layer two additional layers are added. First comes the chemical bath deposited CdS buffer layer, which forms the crucial interface to the absorber layer. It only has a thickness of 50 nm, is n-type and has a doping density of nominally 1e16 cm<sup>-3</sup>. Thus, when the pn-junction forms the buffer layer will be completely depleted of carriers.

On top of the buffer layer comes the TCO, which is the window layer. It is conductive enabling it to collect the carriers laterally while at the same time it is transparent such that photons can penetrate the window layer in order to get absorbed in the absorber layer. If not stated otherwise the TCO in general is a double layer of intrinsic ZnO (i:ZnO) and Al doped ZnO (Al:ZnO or AZO). The i:ZnO layer is deposited to add an artificial series resistance in order to reduce  $V_{oc}$  losses due to lateral inhomogeneities of the saturation current density  $J_0$  [46, 47]. The AZO layer acts as the n<sup>+</sup> layer and as the front contact of the solar cell.

A grid is e-beam evaporated on top of the AZO layer for better current collection. It consists of a roughly 10 nm thick Ni layer and a 2-3  $\mu$ m thick Al layer. In general a 2  $\mu$ m thick Al layer is enough to yield a sufficient small resistance for good carrier collection. However, for some devices the thickness was increased to obtain a stronger grid which helps to contact the solar cell via bonding.

For our champion devices the AZO layer is replaced by a biased ZnO layer. The biased ZnO layer is characterized by a lower doping but higher electron mobility. It therefore has less absorption in the near infrared region while conserving the same sheet resistance compared to the AZO layer [48].

### 2.2.2. Bandalignment

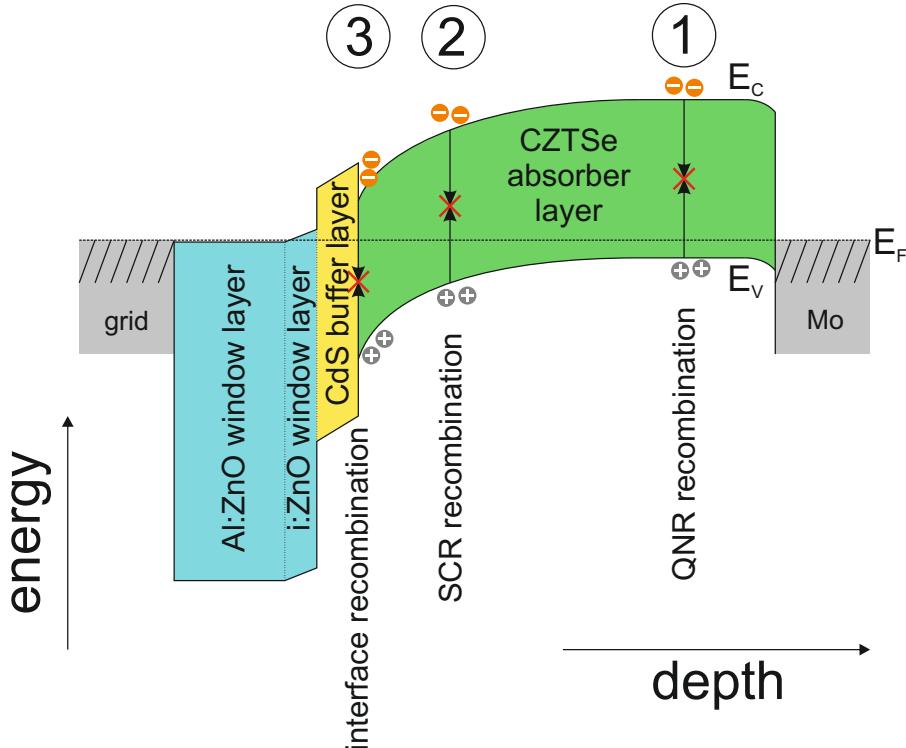

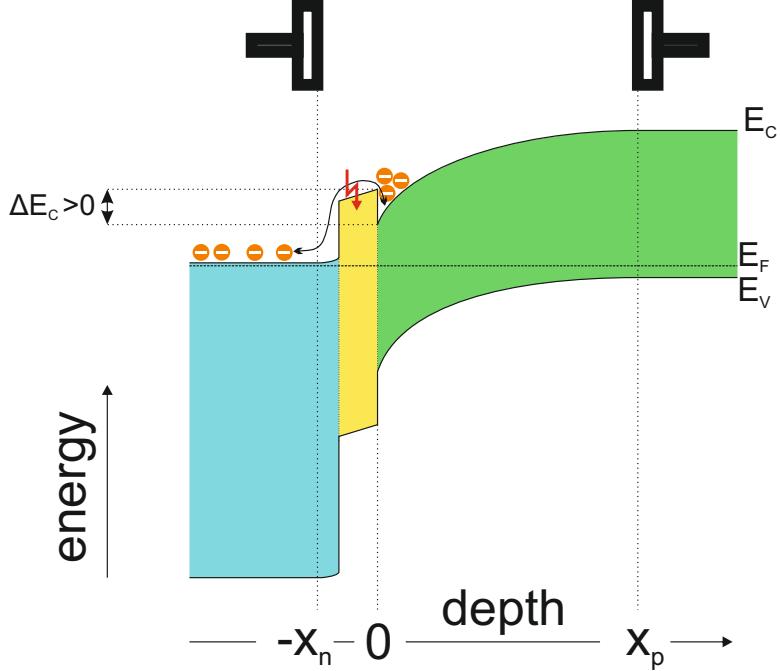

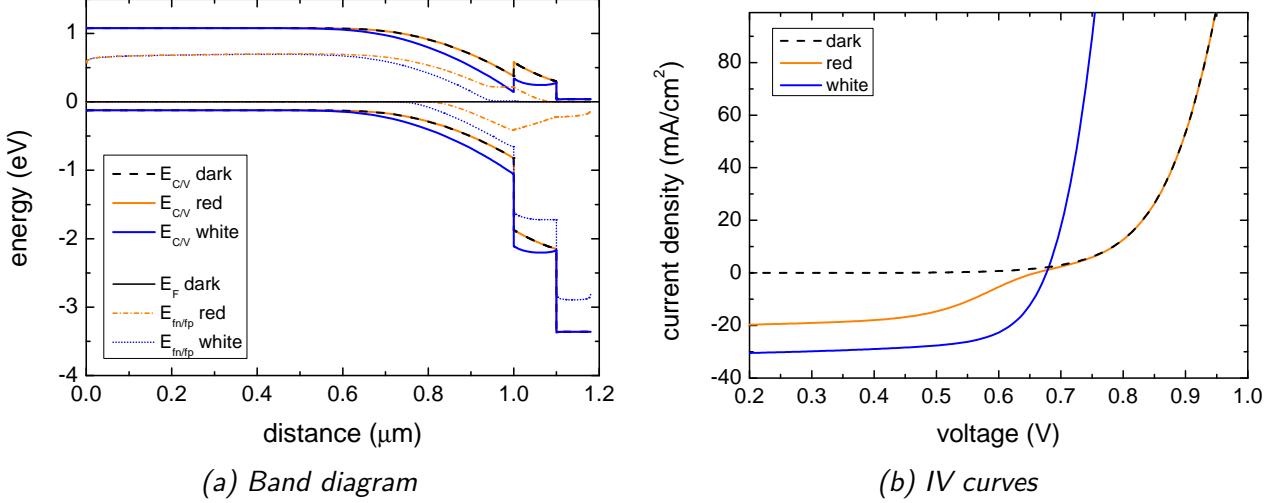

**Figure 2.3.: Band diagram of a CZTSe solar cell** - Possible band diagram for the structure of a solar cell device. Assumed is a conduction band spike at the absorber-buffer interface as well as a small back barrier.

The more complex solar cell structure compared to a  $n^+p$  junction goes along with a more complex band diagram compared to a Schottky contact. A possible band diagram is shown in Fig. (2.3). Except the SLG substrate it contains all the layers as shown in Fig. (2.2a). It needs to be pointed out that this alignment only represents one possibility. It is depicted with a positive conduction band offset  $\Delta E_C > 0$  and a back barrier, which might exist at the CZTSe/Mo interface [49].

According to Ref. [50], the conduction band offset is defined as  $\Delta E_C = E_C^l - E_C^s$ , where  $E_C^l$  and  $E_C^s$  stand for the energy of the conduction band minimum of the semiconductor with the large and the small bandgap, respectively. The values of  $E_C$  itself is given by the electron affinity  $\chi$  of the semiconductor. In the same way as the conduction band offset, the valence band offset is defined:  $\Delta E_V = E_V^s - E_V^l$ . The band alignment featuring  $\Delta E_C > 0$  is said to have a conduction band spike, while a negative band offset  $\Delta E_C < 0$  is said to have a conduction band cliff. For this structure in this work the large and small bandgap semiconductor is CdS with  $E_g = 2.4$  eV [50] and CZTSe with a bandgap of roughly 1 eV [51].

Experimentally there are no direct or indirect measurements for the band offset between CZTSe and CdS. Only for the sulphur containing compound CZTS there are measurements showing a cliff-like alignment [52–54]. However, for CZTSe there are indications of a conduction band spike as deduced from electrical measurements [55], from UPS measurements [56] and from theoretical calculations [57]. In general, for thin film solar cell devices a conduction band spike is favourable only if  $\Delta E_C$  is not exceeding 0.3 eV [58]. For higher conduction band offsets

## 2. Fundamentals of solar cell devices

the spike acts as a barrier for photo generated electrons from the absorber layer. In fact, the limiting current density over a conduction band spike assuming thermionic emission is given by [50, 58]:

$$J_{0,TE} = \frac{1}{4q\nu_n} n_{a,z=0} \exp\left(-\frac{\Delta E_C}{kT}\right). \quad (2.11)$$

$n_{a,z=0}$  gives the density of free electrons at the interface. Thus, to pass a certain current density over a given conduction band spike  $\Delta E_C$  requires a sufficient high density of free electrons at the interface, which is accomplished by a good inversion layer. An inversion layer (in the absorber) at the CdS/CZTSe interface means that minority carriers in the bulk of the absorber become majority carriers at the interface [59]. This property is given for a Fermi level which is closer to the conduction band than to the valence band (see Fig. 2.3). For a good inversion layer it is required that the doping level of the absorber layer is not too high. If the doping density is low enough, the built in potential drops mainly in the absorber layer (see section 2.1) and thus inverts the surface. The beneficial effect of an inversion layer also affects the recombination at the interface and will be discussed in section 2.3.1.

The band offset between the buffer and the window layer is also not allowed to be too large as it can act as a barrier for the diode current [50]. However, the window/buffer band offset will not be discussed here, as it is not object of the experimental section.

## 2.3. IV analysis

An IV curve in general is described by the 1-diode model, where the current density  $J(V)$  expresses as:

$$J(V) = J_0 \left[ \exp\left(\frac{q(V - r_s J)}{AkT}\right) - 1 \right] + \frac{V - r_s J}{R_{sh}} - J_{ph}. \quad (2.12)$$

$J_0$  is the saturation current density,  $r_s$  the series resistance,  $R_{sh}$  the shunt resistance,  $A$  the diode quality factor,  $k$  the Boltzmann constant and  $T$  the temperature. The saturation current density is thermally activated with an activation energy  $E_A$  and can be written in the form

$$J_0 = J_{00} \exp\left(-\frac{E_A}{AkT}\right) \quad (2.13)$$

where  $J_{00}$  is the reference current density. Depending on the recombination pathway different values for  $J_{00}$ ,  $E_A$  and  $A$  are obtained. A complete overview is given in [50]. At open circuit conditions and assuming  $V_{oc}/R_{sh} \ll J_{ph}$ , Eqn. (2.16) can be resolved with respect to  $V_{oc}$  and reads

$$V_{oc} = \frac{E_A}{q} - \frac{AkT}{q} \ln\left(\frac{J_{00}}{J_{ph}}\right). \quad (2.14)$$

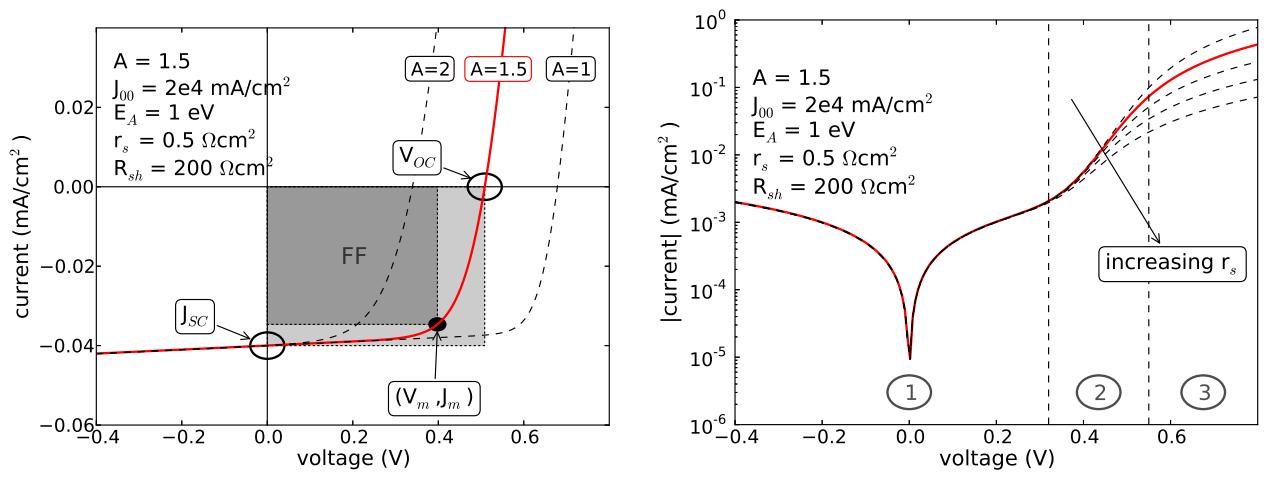

From this equation it is evident that the three parameters  $E_A$ ,  $A$  and  $J_{00}$  are important parameters responsible for the  $V_{oc}$  of the solar cell.  $E_A$  directly affects the  $V_{oc}$ , while  $A$  and  $J_{00}$  are multiplicative factors additionally reducing the  $V_{oc}$ . Note that  $J_{00}$  is generally much larger than  $J_{sc}$  [60, 61] and thus  $\ln(J_{00}/J_{ph}) > 0$ . An effect of the diode quality factor on  $V_{oc}$  is simulated and shown in Fig. 2.4a for three different values of  $A$  while keeping the rest of the

parameters constant.

### 2.3.1. Recombination processes

Three different recombination processes are shown in Fig. (2.3), which can occur in our solar cell devices and can be described by [50]:

$$J_{\text{diode}} = qD_n \left. \frac{dn(x)}{dx} \right|_{x=x_p} + q \int_{x_p}^0 (U_n(x) - G_0(x)) dz + J_{\text{diode, IF}}. \quad (2.15)$$

$D_n$  is the electron diffusion coefficient,  $G_0(x)$  the thermal generation rate and  $U_n(x)$  the recombination rate. The right hand side of Eqn. (2.15) describes the three contributions to the diode current  $J_{\text{diode}}$  from the quasi neutral region (QNR)  $J_{\text{diode,QNR}}$ , from the SCR  $J_{\text{diode,SCR}}$  and from the absorber/buffer interface  $J_{\text{diode,IF}}$ . The contribution due to back surface recombination is neglected due to low minority carrier diffusion lengths in CZTSe absorber layers [14]. The voltage and temperature dependence of each of these contributions can be described by an exponential form like

$$J = J_0 \left[ \exp\left(\frac{qV}{AkT}\right) - 1 \right] \quad \text{with} \quad J_0 = J_{00} \exp\left(\frac{-E_A}{AkT}\right). \quad (2.16)$$

The exponential voltage dependence of the diode current results from the exponential voltage dependence of the carrier densities, which governs the recombination rates.

Eqn. (2.16) contains three parameters, which are specific for different recombination mechanisms.

- diode quality factor  $A$ : The diode quality factor  $A$  describes the voltage dependence of the diode current. It depends on the type of recombination and where the carriers recombine (i.e. interface, SCR or QNR). An overview about the diode quality factors and their temperature dependencies is given in Ref. [50].

- activation energy  $E_A$ : The activation energy  $E_A$  represents the activation of the saturation current density  $J_0$  and therefore the temperature dependence of the diode current. For a good heterojunction the activation energy is given by the absorbers bandgap. However, due to a conduction band miss alignment or Fermi level pinning also lower activation energies are possible for recombination at the interface [62].

- reference current density  $J_{00}$ : The prefactor of the saturation current density is specific for different recombination processes. Especially for tunnelling enhanced recombination the value of  $J_{00}$  can be strongly increased, and therefore significantly increases also  $J_0$ . An overview about values of  $J_{00}$  dependent on the different recombination processes is given in Ref. [50] Tab. 2.2.

All three recombination processes shown in Fig. (2.3) happen in parallel. However, dependent on the value of  $J_0$  (due to the parameters  $J_{00}$ ,  $E_A$  and  $A$ ) one recombination process can dominate over the others and thus gives the diode current  $J_{\text{diode}}$ . Still, due to different voltage dependencies it is still possible that a process with a high diode quality factor dominates at low voltages, while another process with a small diode quality factor dominates at higher voltages.

## 2. Fundamentals of solar cell devices

Radiative recombination in the QNR is the recombination which ultimately limits the solar cell performance via the Shockley-Queisser limit [8]. However, this recombination process is not the limiting process for thin film solar cells. For instance for CIGSe based solar cells the radiative lifetime was found to be  $\tau_{rad} \approx 1\mu s$ , while measured lifetimes are of the order of  $ns$  [63]. Thus, for the compound CIGSe the radiative recombination is not limiting the solar cell performance. Also for the compound CZTSSe measured lifetimes are below  $10\text{ ns}$  [14, 17, 64] and thus excludes radiative recombination to be responsible for limiting the performance of these devices.

We therefore focus on non-radiative recombination via deep defect states - the Shockley-Read-Hall recombination [65, 66].

### 2.3.2. Shockley-Read-Hall recombination

Shockley-Read-Hall (SRH) recombination is the recombination of carriers via localized states within the bandgap. In that case the recombination rate can be written as [50]

$$R_{SRH} = \frac{np - n_i^2}{\gamma_p(n + n^*) + \gamma_n(p + p^*)}, \quad (2.17)$$

where  $n^*$  and  $p^*$  are auxiliary carrier densities which would be realized if the Fermi level were at the defect level. In the absence of tunneling enhanced recombination  $\gamma_p$  and  $\gamma_n$  are the minimum carrier lifetimes  $\tau_{p,0}$  and  $\tau_{n,0}$  for holes and electrons respectively and defined as

$$\tau_{p,0} = (\sigma_{p,0} v_{p,0} N_t)^{-1} \quad \text{and} \quad \tau_{n,0} = (\sigma_{n,0} v_{n,0} N_t)^{-1} \quad (2.18)$$

$\sigma_{p/n}$  and  $v_{p/n,0}$  is the capture cross section and the thermal velocity for holes/electrons and  $N_t$  is the number of trap sites per unit volume. Taking also tunnelling enhanced recombination into account, the quantities  $\gamma_p$  and  $\gamma_n$  contain an additional factor, accounting for an increased carrier density at the trap site. These quantities can be expressed as [67]:

$$\gamma_p = \tau_{p,0} (1 + \Gamma_p)^{-1} \quad \text{and} \quad \gamma_n = \tau_{n,0} (1 + \Gamma_n)^{-1} \quad (2.19)$$

From Eqn. (2.19) it becomes evident that the locally increased carrier density due to tunneling results in lowered lifetimes for the free carriers.

As mentioned above, recombination can occur in the SCR, in the QNR and at the heterointerface. Now I will discuss briefly the impact of the region of recombination on the diode parameters, in the case of SRH recombination.

#### 2.3.2.1. SCR recombination

Based on Eqn. (2.17) the SRH recombination rate takes its maximum at the position where  $\tau_{p,0}^{-1}p = \tau_{n,0}^{-1}n$  and therefore is located in the SCR. For SRH recombination in the SCR the diode quality factor equals 2. The picture behind a diode quality factor of 2 is that at the point of maximum recombination, where  $\tau_{p,0}^{-1}p = \tau_{n,0}^{-1}n$ , the quasi Fermi levels move symmetrically with respect to the defect level. Therefore, each Fermi level moves  $qV/2$  and thus  $A = 2$ .

However, assuming an exponential defect distribution [68], also voltage independent diode quality factors between 1 and 2 are possible.

Considering additionally tunnelling enhanced recombination, diode quality factors above 2 are possible [69]. Tunnelling enhanced recombination not only alters the diode quality factor

but also deteriorates  $J_0$  via  $J_{00}$ . The contribution due to tunnelling on  $J_0$  gets severe at room temperature for doping densities  $N_A > 2e16 \text{ cm}^{-3}$  [50].

For all recombination processes in the SCR the activation energy of  $J_0$  is always equals the absorber bandgap  $E_g$ . Even in the case of tunnelling enhanced recombination an activation energy of  $E_g$  is obtained as it only increases the number of free carriers at the site of recombination. Thus, as already mentioned, increases the saturation current density.

### 2.3.2.2. QNR recombination

However, even though the maximum of recombination happens in the SCR, the diode current can still be dominated by recombination in the QNR. Dominated QNR recombination occurs for sufficient high carrier lifetimes so that the carriers first drift out of the SCR before they recombine [50]. For recombination in the QNR the diode factor equals 1 as long as the bias voltage is not too large, such that the condition of low injection is still fulfilled. Under low injection conditions the majority quasi Fermi level stays roughly constant and only the minority quasi Fermi level moves with respect to the voltage, which is  $qV$ ; thus,  $A = 1$ . Evidently, as for SCR recombination the activation energy is given by the absorbers bandgap.

### 2.3.2.3. Interface recombination

The recombination processes discussed above all yield an activation energy of  $J_0$  equal to the bandgap. However, due to recombination via deep defect states at the interface also activation energies below  $E_g$  can occur for certain scenarios.

For the following considerations we only take an asymmetric  $n^+p$  junction into account and recombination via deep defect states. For the  $n^+p$  junction the electrons are majority carriers at the interface and thus we write  $n_{\text{IF}} \gg p_{\text{IF}}$ . Eqn. (2.17) can then simplified to

$$R_{SRH} = p_{\text{IF}} \gamma_p^{-1} = p_{\text{IF}} S_p, \quad (2.20)$$

where  $S_p$  denotes the surface recombination velocity. For this case there are then two reasons for a lowered activation energy than the absorber band gap:

One reason is a conduction band cliff, i.e.  $\Delta E_C < 0$ . For this scenario we assume that cross recombination is possible, i.e. electrons of the buffer layer can recombine with holes of the absorber layer. This results in a reduced interface bandgap  $E_{g,IF} = E_g + \Delta E_C$ , with  $\Delta E_C \leq 0$  [62] and therefore the activation energy is lowered compared to the absorbers bandgap.

The second reason for a reduced activation energy is a pinned quasi Fermi level of the majority carriers at the interface. For a  $n^+p$  junction this is the electron quasi Fermi level. Then the electron concentration at the interface is constant and does not change with bias voltage. The activation energy is given by temperature independent quantity  $\Phi_b^p$ , which is the energetic distance of the absorber valence band to the hole quasi Fermi level at the interface. Experimentally, this activation energy can be deduced by temperature dependent IV (IVT) measurements and Eqn. (2.14). IVT measurements will be discussed in section 6.1.

## 2.3.3. Solar cell parameters

In section 2.3 I have discussed the three parameters  $E_A$ ,  $A$  and  $J_{00}$  describing the diode current. However, in order to characterize the efficiency of the solar cell, there is a set of parameters directly available from the measurement, namely the open circuit voltage  $V_{oc}$ , the short circuit

## 2. Fundamentals of solar cell devices

current density  $J_{sc}$ , the fill factor  $FF$  and the power conversion efficiency  $\eta$ .  $J_{sc}$  gives the photo current at zero applied bias voltage and  $V_{oc}$  is the voltage in open circuit conditions, when no current flows. With the current density  $J_m$  and the voltage  $V_m$  at the maximum power point, the  $FF$  is defined as

$$FF = \frac{V_m J_m}{V_{oc} J_{sc}}. \quad (2.21)$$

The (power conversion) efficiency is defined as the ratio of the generated electrical power and the incoming power as

$$\eta = \frac{P_{out}}{P_{in}} = \frac{V_m J_m}{P_{in}} = \frac{FF V_{oc} J_{sc}}{P_{in}}. \quad (2.22)$$

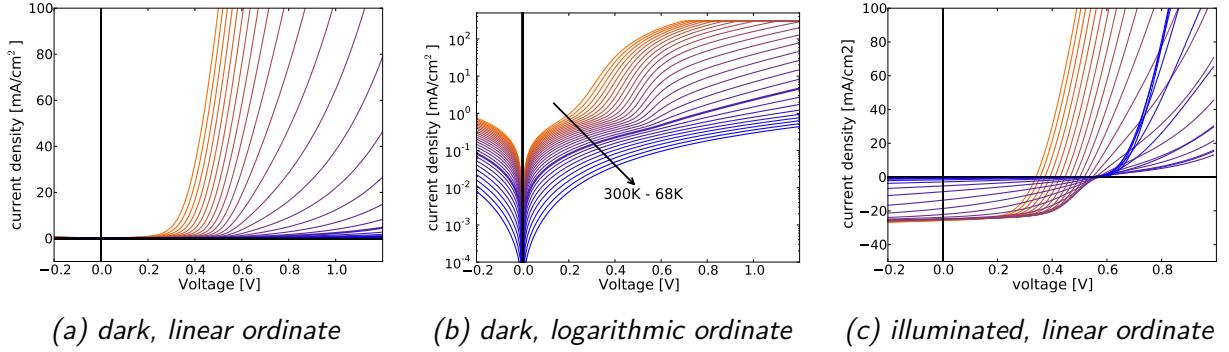

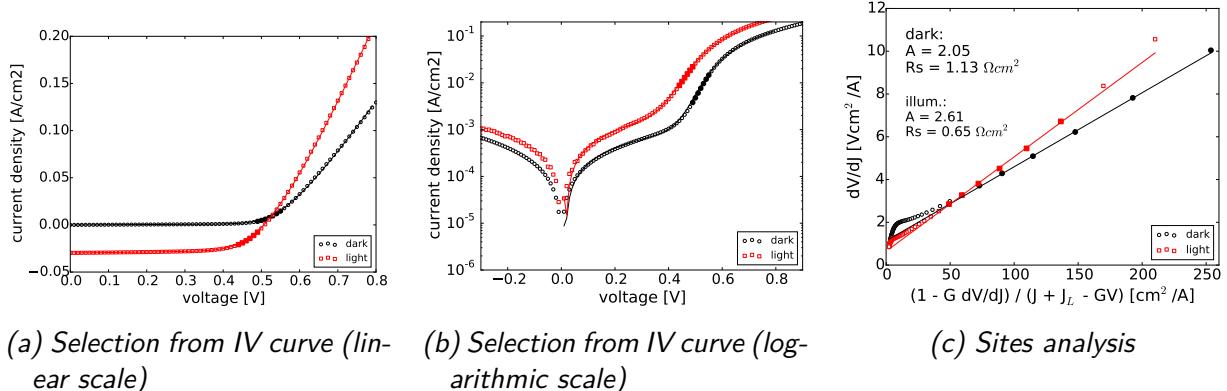

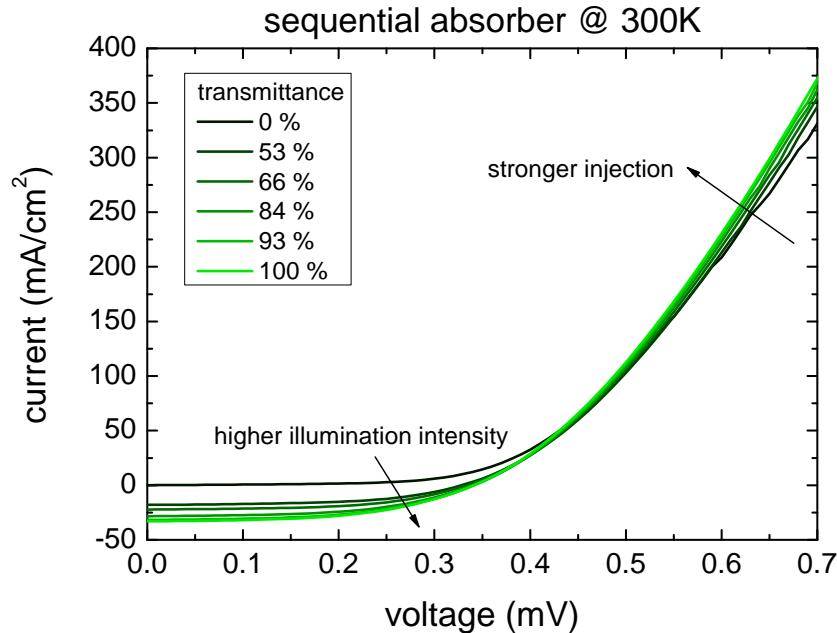

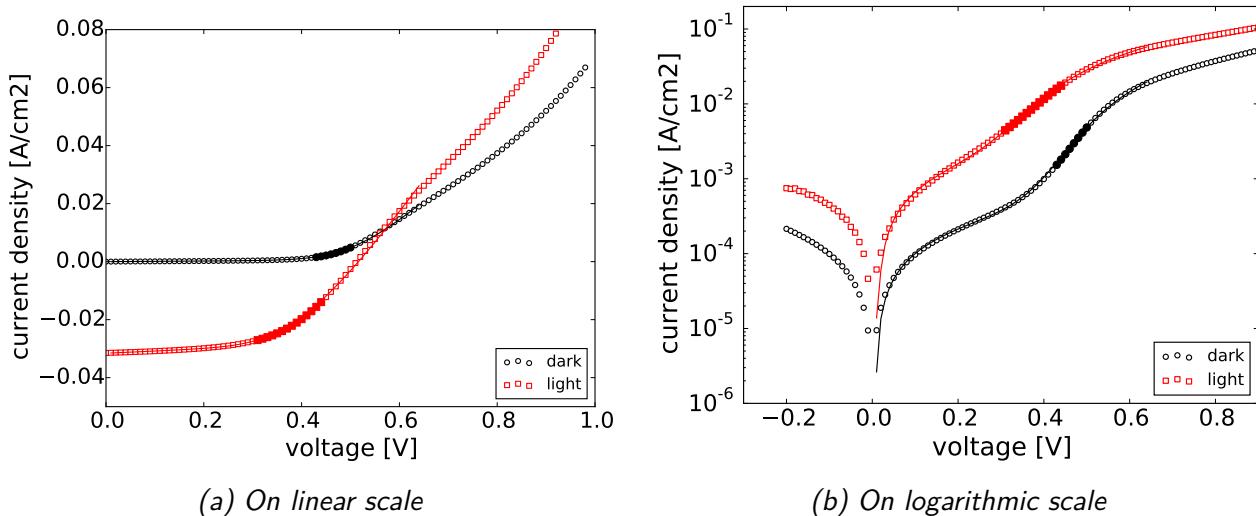

A simulated IV curve according to Eqn. (2.12) is shown in Fig. (2.4a). Annotated are the points at  $V_{oc}$  and at  $J_{sc}$ . From this image the FF is defined as the ratio of the area of the light grey rectangle and the dark grey rectangle and therefore can be pictured as the squareness of the IV curve. Also shown as dashed lines are IV curves with diode quality factors of 1 and 2. The effect on the IV curve is a lowered  $V_{oc}$  according to Eqn. (2.14) as well as the voltage dependence of the exponential function. This can be seen by the current onset of the exponential function, which is more abrupt for  $A = 1$  compared to  $A = 2$ . In Fig. (2.4b) the same IV curve is shown on a logarithmic ordinate with the same set of parameters (solid red line). From this graph three regions can be made out. The first region 1) is dominated by the shunt resistance and therefore is present as a logarithmic function on the logarithmic scale. The second region 2) represents the diode as a straight line with a slope of  $1/AkT$ . This region is only apparent if the series resistance is not too high. The third region 3) in far forward bias is dominated by the series resistance. With a logarithmic scale the presence of a series resistance is seen by the bending of the IV curve from the straight line of region 2).

### 2.3.3.1. Determination of solar cell parameters

There exist several methods on how to extract the solar cell parameters from a measured IV curve. In this section I will focus on two methods, to which I will refer later on for the determination of the IV parameters.

**iv-fit** This method fits the measured IV curve to Eqn. (2.12) [70]. It needs to be pointed out that a orthogonal-distance regression is used in order to account for the strongly varying slope of the IV curve.

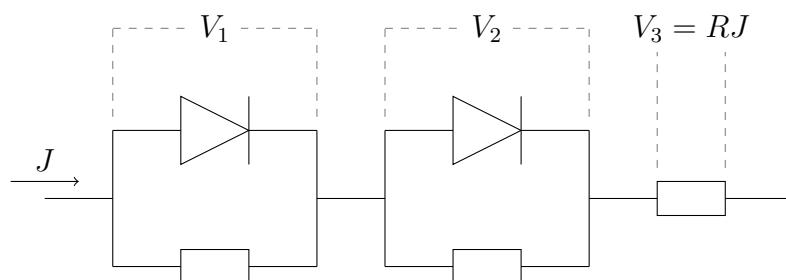

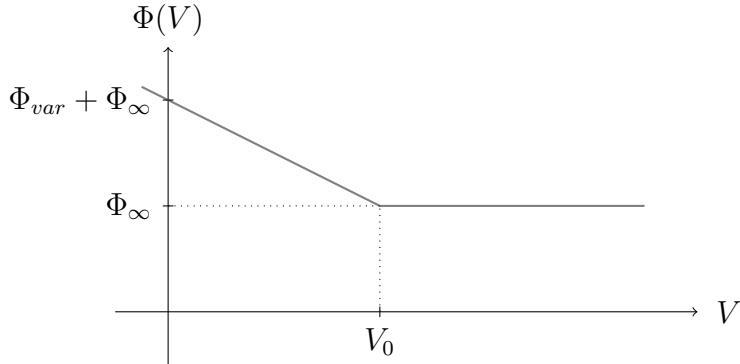

**Sites-method** This method was first introduced by Sites and Mauk [71] and later extended by Hegedus and Shafarman [72]. It relies on the certain approximations and manipulations of Eqn. (2.12) such that in consecutive plots the IV parameters are obtained. However, in order to correctly account for the shunt resistance for the determination of  $r_s$  and  $A$ , the formula used in [71] needs to be used and not the one given in Ref. [72]. The derivation is given in appendix (A). The actual determination of the IV parameters was done by a Python script and is discussed in detail in section A.2.

For both methods only the saturation current density  $J_0$  is obtained. In order to also get the values for  $J_{00}$  and  $E_A$ , temperature dependent measurements are necessary, as discussed in section 6.1.

(a) Solid red line according to parameters given in the figure. Dashed black lines are IV curves with diode quality factors of 1 and 2.

(b) Variation of the series resistance  $r_s$ . Solid red line is simulated with the same parameters as in Fig. (2.4a) but without a photo current.

**Figure 2.4.: Simulation of IV curves** - Simulation according to Eqn. (2.12). Annotated are the quantities  $V_{oc}$ ,  $J_{sc}$  and  $FF$ . The dashed lines show IV curves with the same set of parameters but with a diode quality factor of 1 and of 2. The maximum power point is denoted as  $(V_m, J_m)$ , Fig. (2.4a). Fig. (2.4b) shows the IV curve on a logarithmic scale with a variation of the series resistance.

---

CHAPTER

**THREE**

---

## GROWTH OF THE CZTSE ABSORBER LAYER

The growth of the CZTSe absorber layer is described in this chapter. It is divided in two sections: section 3.2 is dedicated to the sequential process and section 3.3 to the high temperature co-evaporation process. Both techniques have in common that the materials (Cu, Zn, Sn, Se) are deposited by co-evaporation in an molecular beam epitaxy (MBE) chamber. This system is described in section 3.1. Section 3.5 compares the differences in microstructure arising from the different growth techniques by polished SEM and TEM images.

### **3.1. PVD system**

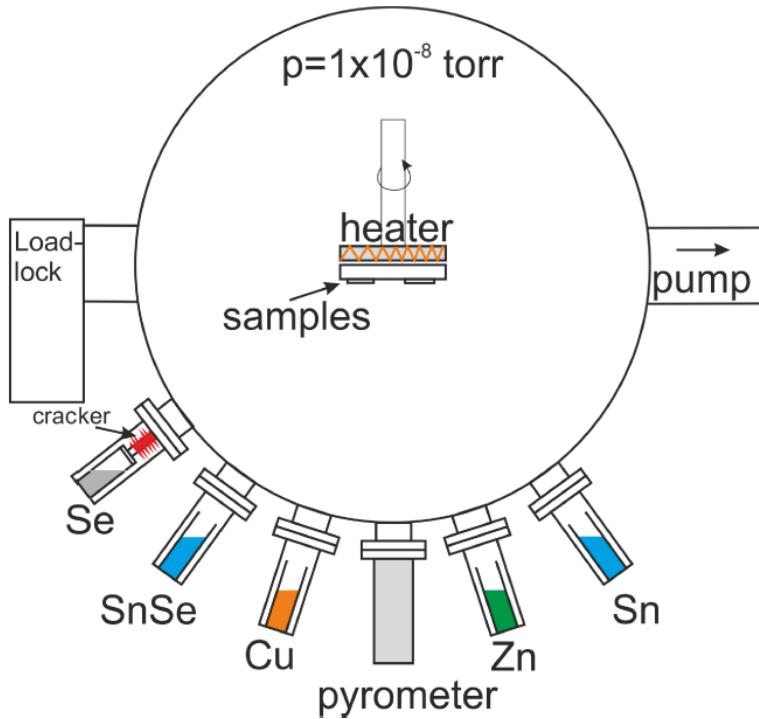

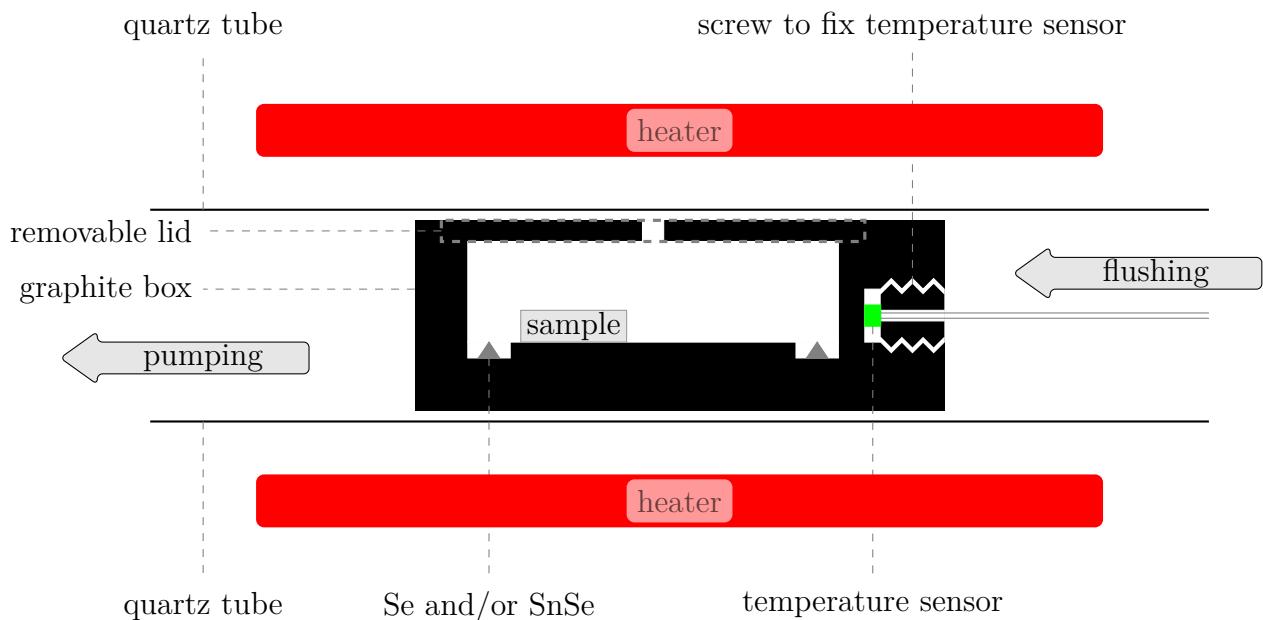

Precursor (section 3.2) and absorber (section 3.3) layers are grown in an MBE chamber, which is sketched in Fig. (3.1). SnSe, Cu, Zn and Sn are evaporated from effusion cells and Se is supplied by a valved cracker source. Elemental fluxes were controlled by changing the bulk temperature of the sources and measured by a quartz crystal monitor and a Bayard Alpert pressure gauge.

The sample chamber is pumped by a turbo molecular pump and additionally cooled with liquid nitrogen to achieve a pressure (during growth) of  $\sim 10^{-8}$  torr. The sample holder is rotated during growth to improve homogeneity and can be heated as indicated in Fig. (3.1). Four inch  $\times$  inch substrates can be mounted into the sample holder. Thus four identical absorber/precursor samples are obtained from each process run. A pyrometer with a detection range from  $2 \mu\text{m}$  to  $2.6 \mu\text{m}$  measures the temperature of the substrate and allows *in-situ* process control. Also diffuse laser light scattering (LLS) is measured during the growth processes, but will not discussed in this thesis. Details about growth monitoring by LLS can be found for example in Refs. [19, 73].

### 3. Growth of the CZTSe absorber layer

**Figure 3.1.: MBE chamber** - For deposition of CZTSe precursor and absorber layers. Included are SnSe, Cu, Zn and Sn effusion cells. Se is supplied by a valved cracker source. Image taken with permission from Alex Redinger (unpublished).

## 3.2. Sequential process

The solar cells fabricated from absorbers processed with a sequential process are described in this section. Section 3.2.1 explains the difficulties in growing high quality kesterite layers and gives a motivation for the sequential process. The growth of two different kinds of precursors is presented in section 3.2.2 and section 3.2.3. The high temperature annealing procedure needed for a good crystal structure is described in section 3.2.4.

### 3.2.1. Decomposition reaction

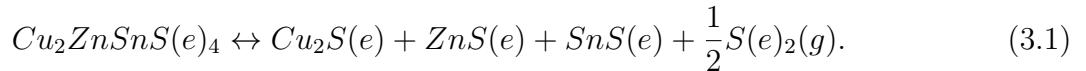

One problem which occurs at high temperatures is the decomposition reaction of the kesterite phase given in Eqn. (3.1) [74, 75]:

This equation also holds if the chalcogen species S is replaced with Se (thus the notation of  $S(e)$ ) in order to obtain CZTSe [76]. As I am dealing in this thesis with pure Se based absorbers, the discussion in the following is based on CZTSe. From Eqn. (3.1) it follows that Se is lost from the film. Due to the high vapour pressure of SnSe at these temperatures [77], also Sn losses are expected [78]. In order to prevent the decomposition reaction, a SnSe and Se vapour pressure needs to be supplied to keep the reaction in equilibrium, i.e. shift the reaction to the left hand side.

Thus, based on these considerations of the decomposition reaction which can occur at high

temperatures motivates the approach of a sequentially processed absorber layer: First, a precursor is grown at low temperatures, where no elemental losses from the film are observed [79]. In a second step this precursor is annealed at high temperatures - with the addition of Se and SnSe into the annealing chamber a Se and SnSe partial pressure is created to prevent the decomposition reaction (3.1). These high vapour pressures of SnSe and Se cannot easily be supplied in a PVD chamber.

Another decomposition reaction of the kesterite phase which was proposed in literature is the back contact reaction with Mo [80, 81]. It suggests that the CZTS/Mo interface is thermodynamically not stable at the commonly applied annealing temperatures ( $> 500$  °C) and thus decomposes. The result is that a  $\text{MoS}_2$  layer and secondary phases form at the back contact. However, a study by Shin *et al.* [82] on pure Se based absorbers shows that the formation of an intermediate  $\text{MoSe}_2$  layer between CZTSe and Mo is due to the diffusion of Se through the absorber layer and not due to a decomposition reaction. Note that the experiments by Scragg *et al.* [80, 81] were carried out with pure S containing precursors, while Shin *et al.* [82] used pure Se precursors.

The samples which are produced by the sequential process presented here also exhibit a  $\text{MoSe}_2$  layer at the back contact. The thicknesses were determined by polished TEM images and are around 100 nm. However, detrimental effects of the  $\text{MoSe}_2$  layer were observed for thicknesses above 600 nm [83]. Besides, the state-of-the-art CZTSe devices with a 11.6 % efficiency exhibits a  $\text{MoSe}_2$  layer of roughly 200 nm as well [11]. Thus, the formation of the  $\text{MoSe}_2$  layer is not further investigated in the framework of this thesis as it seems not to be detrimental.

### 3.2.2. Precursor growth at 320 °C

The following discussion is based on the growth process by Mousel *et al.* [84]. Besides, the precursors and the resulting absorbers were grown by Marina Mousel as well. However, the sequentially processed solar cells discussed in section 5.5 and 6.2 arise from this growth process, which is therefore described in this section.

The precursor is grown at 320 °C in the PVD chamber at constant fluxes of Cu, Zn, Sn and Se. The precursor growth temperature was kept below 350 °C to prevent expected Sn and Se losses [79]. The precursor was grown under Cu-rich conditions. It is known from CIGSe that a Cu-rich phase in the growth process improves the grain growth, which was also found for the CZTSe compound [9, 84]. A consequence of a Cu-rich precursor growth is that a  $\text{Cu}_{2-\delta}\text{Se}$  phase forms on the surface [84]. This  $\text{Cu}_{2-\delta}\text{Se}$  phase needs to be etched by KCN [85] prior to annealing to obtain working solar cell devices. Otherwise a detrimental Cu-Sn-Se phase forms on the surface during annealing [86]. After the KCN etch, the precursors shift to a Cu-poor composition due to the removal of the copper selenide layer [84]. These resulting Cu-poor precursors are subsequently annealed following the high temperature annealing process as described in section 3.2.4.

### 3.2.3. Precursor growth at low temperatures

Similar to the deposition of the precursor described in the previous section, the growth temperature can even be lowered. The heater of the sample holder was switched off during the growth process of these precursors. Nevertheless, heating still occurs from the sources itself. The tip temperature of the Cu and Sn evaporation sources is around 1300 °C. This means that

### 3. Growth of the CZTSe absorber layer

the samples are radiatively heated from the sources. The exact sample temperature cannot be estimated and is assumed to be around 100 °C.

A motivation of this process is to grow a precursor layer which is as homogeneous as possible and to reduce the segregation of secondary phases. Besides, the highest efficiency for pure Se based absorber layers are currently obtained from a sequential process with a growth temperature of the precursor of 150 °C [11].

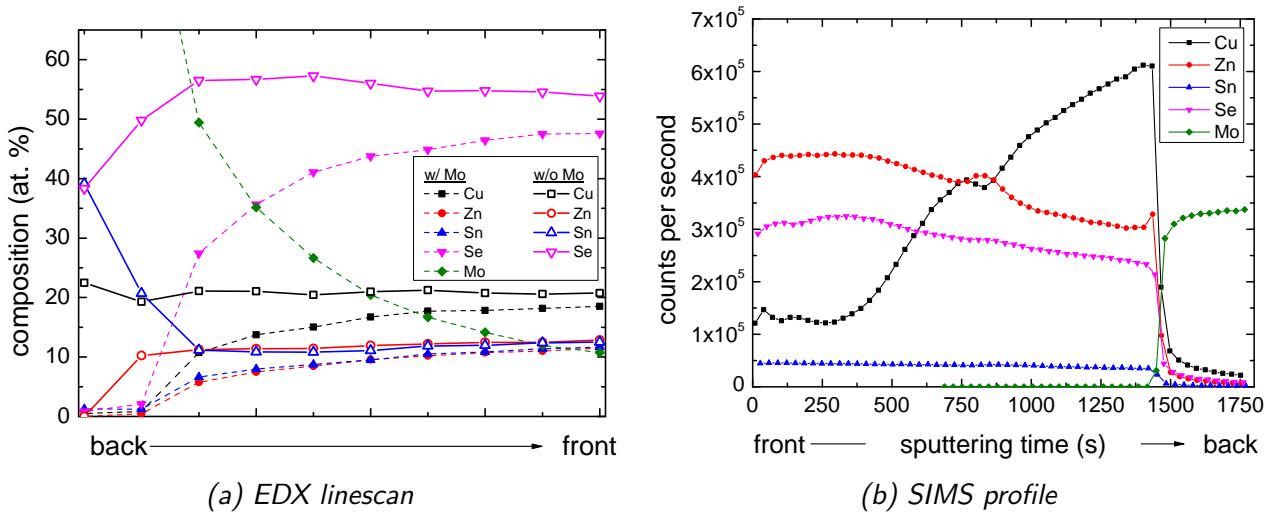

Fig. (3.2) shows the compositional depth profile of a precursor measured by an EDX cross sectional linescan (Fig. (3.2a)) and by secondary ion mass spectroscopy (SIMS) (Fig. (3.2b)).

Full symbols/dashed lines in Fig. (3.2a) show the compositional depth profile when the Mo peak is taken into account for the evaluation of the EDX data. The Mo peak is seen throughout the sample thickness due to the interaction volume of the electron beam. Thus, the same data was evaluated without taking the Mo peak into account (open symbols, solid lines). From this data a homogeneous in-depth composition can be deduced. The SIMS profile in Fig. (3.2b) shows a rather homogeneous Zn, Sn and Se concentration, while a strong gradient is observed for the Cu concentration. However, the exact same Cu gradient was obtained when the sample was ripped off from the substrate and measured from the back to the front surface. Therefore, it is concluded that the strong Cu gradient in the SIMS profile is an artefact of the measurement. A possible explanation could be that the sputtering process promotes the diffusion of Cu atoms deeper into the film resulting in such a Cu profile. Such a phenomenon is not observed for the samples grown at 320 °C [84] and could be due to the amorphous structure of the precursor film (due to the low growth temperature). In conclusion:

1. The SIMS profiles are not reliable for these kind of precursors due to artefacts of the measurements.

2. EDX linescans indicate a homogeneous compositional depth profile.

#### 3.2.4. High temperature annealing

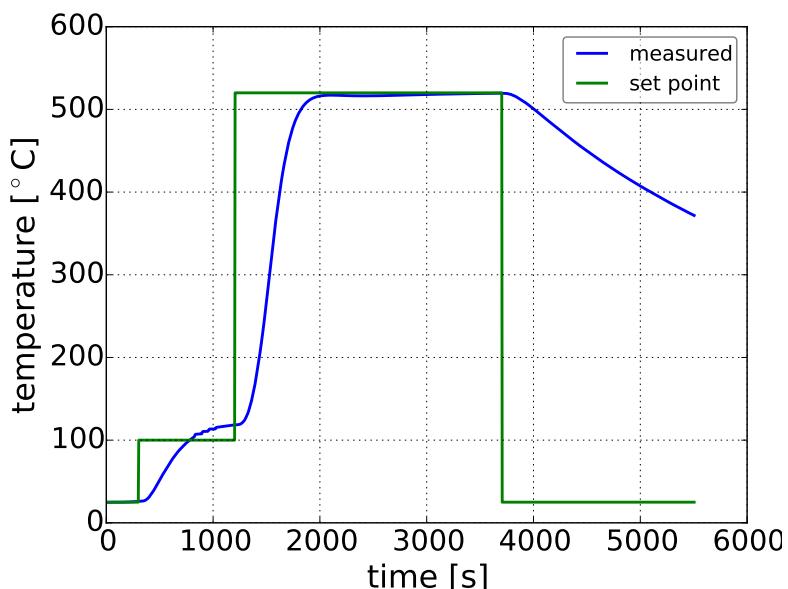

In order to form the kesterite crystal structure, the precursors need to be heated to high temperatures [78, 87]. This annealing procedure is done in a tube furnace as it is depicted in Fig. (3.3). The sample is placed inside a graphite box, which itself is put into a quartz tube. The quartz tube is heated from the outside as indicated by the heaters (red bars). A thermocouple is pressed with a screw against an inside wall of the graphite box to measure its temperature. Additional Se and SnSe can be placed into the cavities inside the graphite box in order to create a SnSe and Se atmosphere at high temperatures and consequently to prevent the decomposition reaction of CZTSe (see section 3.2.1). The removable lid has a small hole in the middle in order to allow for pumping and flushing of the inside of the graphite box. The sample is not placed directly under the hole as the SnSe and Se atmosphere is expected to be less homogeneous in this area. Indeed, annealed samples show less homogeneity if the sample is placed under the hole, which is visible by eye.

The temperature profile of an annealing process is depicted in Fig. (3.4). The green curves represents the setpoint of the temperature and the blue curve the measured temperature of the thermocouple shown in Fig. (3.3). The annealing process can be described by the following steps:

**Figure 3.2.: Compositional depth profile of low temperature precursor** - (a) shows an EDX linescan across a cross section of a precursor deposited at 100 °C with an acceleration voltage of 7 keV. Analysis was made w/ (solid symbols) and w/o (open symbols) taking the Mo peaks into account. A flat compositional profile is observed when not taking into account the Mo peaks. (b) shows a SIMS profile of the same precursor. A strong Cu gradient is observed from the front to back contact, which is an artefact of the measurement.

**Figure 3.3.: Tube furnace for high temperature annealing process** - Sample is placed inside a quartz tube. Additional Se and/or SnSe can be placed into the cavities of the inside of the graphite box to prevent the decomposition reaction of CZTSe at high temperatures (see section 3.2.1). A temperature sensor is pressed at the wall inside the graphite box in order to determine the temperature of the graphite box.

### 3. Growth of the CZTSe absorber layer

1. Mounting of the sample and additional Sn and SnSe inside the graphite box and evacuating the quartz tube.

2. 4 x flushing with  $N_2$  at room temperature.

3. Heating to 100 °C.

4. 4 x flushing with  $H_2/N_2$ , when the graphite's temperature is above 100 °C.

5. Setting a background pressure of 1 mbar  $H_2/N_2$ .

6. Heating to 520 °C.

7. Annealing at 520 °C for about 30 minutes, i.e. timespan the measured temperature of the graphite box is at 520 °C.

8. Natural cool down to room temperature

**Figure 3.4.: Temperature profile from the high temperature annealing process** - The annealing time at 520 °C is roughly 30 minutes. The measured temperature corresponds to the reading of the thermocouple pressed against the graphite box (see Fig. (3.3)).

Generally, 20 mg of Se powder and 15 mg of SnSe chunks were used to supply the Se and SnSe atmosphere. The powder and chunks were split roughly in half and put into the two cavities of the graphite box.

## 3.3. High temperature co-evaporation

For the growth of the absorber layers described in this section, the substrate temperature is set to high temperatures and thus no additional annealing process is required. In order to prevent the decomposition reaction as described in section 3.2.1, the substrate temperature is set only to 470 °C such that the required Se overpressure does not need to be as high as for the

sequential process <sup>1</sup>. Besides, a SnSe evaporation source is used to stabilize the decomposition 3.1 mentioned in section 3.2.1.

### 3.3.1. Overview of literature processes

In the initial co-evaporation deposition stage only  $ZnSe$  and  $Cu_xSe_y$  forms at the back contact while Sn is not incorporated into the film [73, 79, 88–90]. This phenomenon was also observed for CZTS [91]. Kaune *et al.* [73] suggest that this is related to the detrimental decomposition reaction with Mo. However, the expected thickness of the  $MoSe_2$  layer from this reaction is too large for the decomposition reaction to be the sole reason that Sn is not incorporated in the early stage of the deposition. According to my best knowledge, there is no published study explaining the delayed formation of the kesterite phase. However, as  $Cu_xSe_y$  exists independent on whether Cu-rich ( $Cu/Zn$  flux  $> 1$ ) or Zn-rich ( $Cu/Zn$  flux  $< 1$ ) growth conditions are applied, a possible (liquid-phase assisted [92, 93]) grain growth due to  $Cu_xSe_y$  is possible in both cases [94].

Continuing the deposition process, the  $Cu_xSe_y$  is consumed to form CZTSe [89]. The  $ZnSe$  in contrast is only consumed if the ongoing deposition is Cu-rich enough [94]. Another factor determining the consumption of  $ZnSe$  might be the substrate temperature [89], i.e. at lowered substrate temperatures the diffusivity of atoms reduces such that the buried  $ZnSe$  at the back side cannot react to form CZTSe.

Another approach to reduce the growth of  $ZnSe$  at the back side of the film is a lowered substrate temperature at the beginning of the process [19, 95, 96]. In that case the  $ZnSe$  growth is reduced and the growth of CZTSe is not delayed [95].

It has been shown by Hsu *et al.* that  $ZnSe$  grains at the back contact are not harmful to device performance [94, 97]. Nevertheless, large amounts of  $ZnSe$ , i.e. almost complete layers, diminish the solar cell performance [95, 98].

At the end of the process, the Cu flux is shut down prior to the Zn flux if Cu-rich growth conditions are applied in order to end up with a Cu-poor absorber layer [99]. Additionally, a Zn-rich surface layer is induced which was shown to increase the efficiency of the solar cell [100].

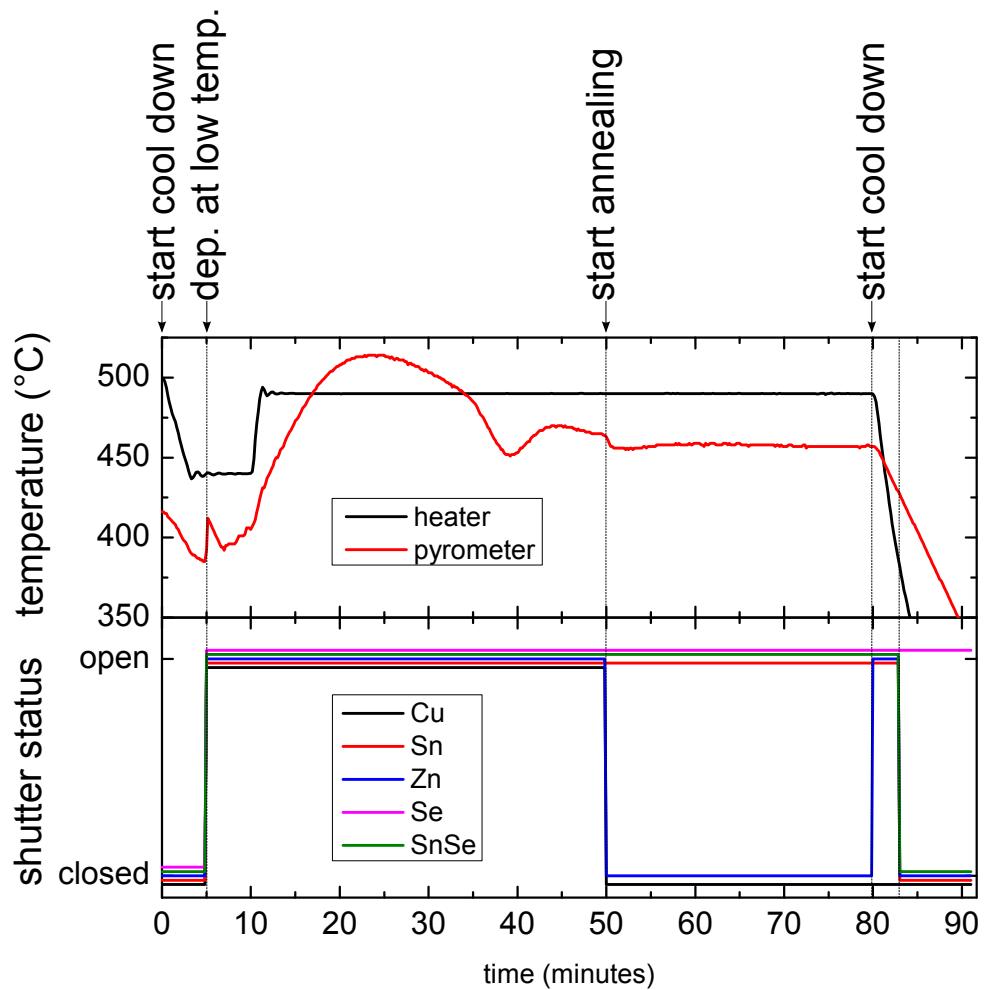

### 3.3.2. Our process

The standard process of the co-evaporated absorber layers used in this thesis is shown in Fig. (3.5). The upper and the lower graph show the temperature profile and the shutter status during the growth process, respectively. The temperature of the evaporation sources were kept constant throughout the deposition process, which results in constant elemental fluxes. In that case the growth conditions are Zn-rich. To increase the reactivity of Se, the cracker is heated to 1000 °C. The substrate is preheated to 500 °C. The process then starts with decreasing the substrate temperature in order to reduce the amount of  $ZnSe$  grains at the back contact, as discussed above. The deposition at low temperatures is carried out for 5 minutes before the heater temperature is increased to 500 °C. The substrate temperature measured by the pyrometer is not constant during the deposition and may vary for example due to changes in secondary phases [99]. The measured temperature by the pyrometer levels off at around 470 °C, which is the referred value of the growth process.

After a deposition time of 45 minutes at a heater temperature of 500 °C, the Cu and the Zn shutter are closed and the sample is annealed in a Sn,  $SnSe$  and Se flux/atmosphere for

<sup>1</sup>Remember that the high temperature annealing is carried out at 520 °C.

### 3. Growth of the CZTSe absorber layer

**Figure 3.5.: Growth process by co-evaporation at high temperatures** - The process can be divided into a growth section (5 minutes - 50 minutes) and an annealing section (50 minutes - 80 minutes). At the beginning of the process, the substrate temperature is lowered to reduce the formation of ZnSe at the back contact [89]. During the first 3 minutes of the cooldown, the Zn shutter is open in order to induce a Zn-rich surface [100].

30 minutes. The sample is cooled to 200 °C after the annealing step. In the first 3 minutes of the cooldown, Zn, Sn, SnSe and Se is supplied. Zn is needed to induce a Zn-rich cap. Repins *et al.* reported that a Zn-rich cap in combination with an air annealing increases the device efficiency [99]. However, the solar cells ended up dead if the absorber layer grown according to the process shown in Fig. (3.5) was air annealed. Still, a Zn-rich cap can favour the formation of ZnSe over SnSe or  $\text{Cu}_x\text{Se}_y$ , which are much more detrimental to solar cell performance [98]. The further cool down in Sn, SnSe and Se atmosphere prevents the decomposition reaction at high temperatures (see section 3.2.1). It was shown by Bishop *et al.* that if the surface is not stabilized during cool, the solar cell efficiency decreases significantly.

The behaviour of the pyrometer was not discussed in literature extensively. Redinger *et al.* interpreted the broad oscillations in terms of interference fringes [19] based on the examination of the *in-situ* laser light scattering signal in Ref. [73]. Mise *et al.* interpreted the first strong rise of the pyrometer signal by an increased emissivity at 2000 nm in the early stage of the deposition. The transition from the minimum around 40 minutes to the subsequent plateau between 45 minutes to 50 minutes was interpreted as the transition from a Cu-rich to a Cu-poor film. As the fluxes in the process shown in Fig. (3.5) were set constant during growth and no intentional Cu-rich step was included, the Cu-rich to Cu-poor transition in the pyrometer could be the point where all the initial formed  $\text{Cu}_x\text{Se}_y$  is consumed. The drop of the pyrometer signal at 50 minutes is linked to the closing of the Cu shutter. The Cu-tip is operated around 1300 °C such that a substantial heating occurs from that source alone leading to an apparent temperature drop after closing the Cu-shutter. An additional loss of reflected infra-red light from the source could also lead to a drop in the pyrometer signal.

### 3.3.2.1. Multi-stage process

A variation of the process described above (section 3.3.2) is the so-called *multi-stage process* [19]. The rather long deposition (45 mins) and annealing (30 mins) period shown in Fig. (3.5) is chunked into several shorter periods of deposition and annealing. A motivation of this process variation is that a higher quality material is formed right away.

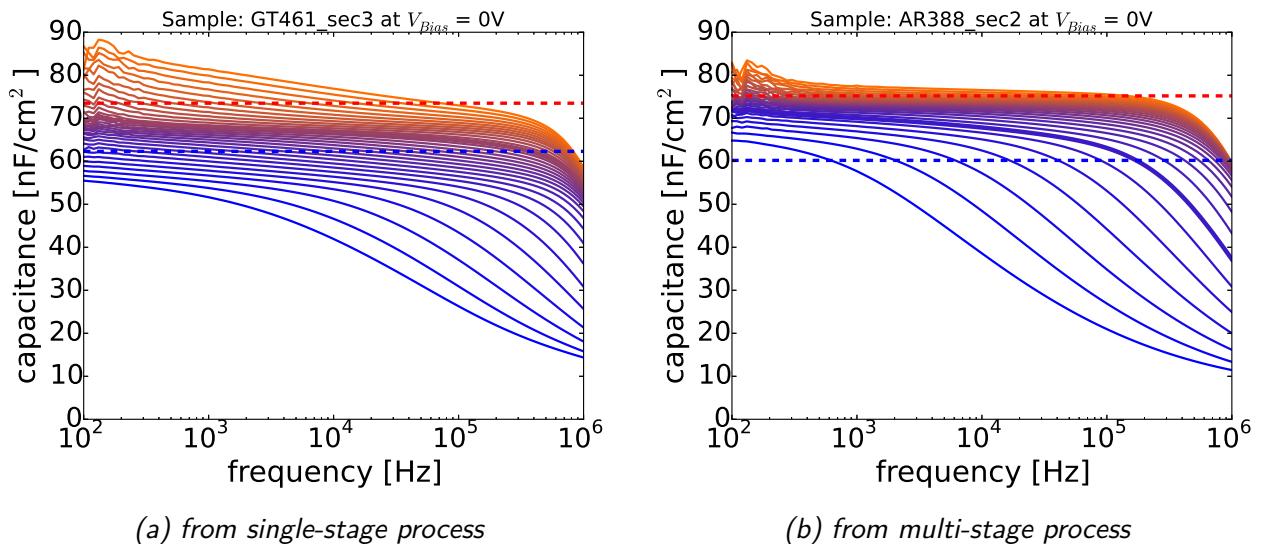

However, solar cell devices generally did not show an improved efficiency. Also the capacitance spectra were similar as mentioned in section 5.6.1. Thus, for most of the devices presented here, the more simple process depicted in Fig. (3.5) was applied for the growth of the absorber layer.

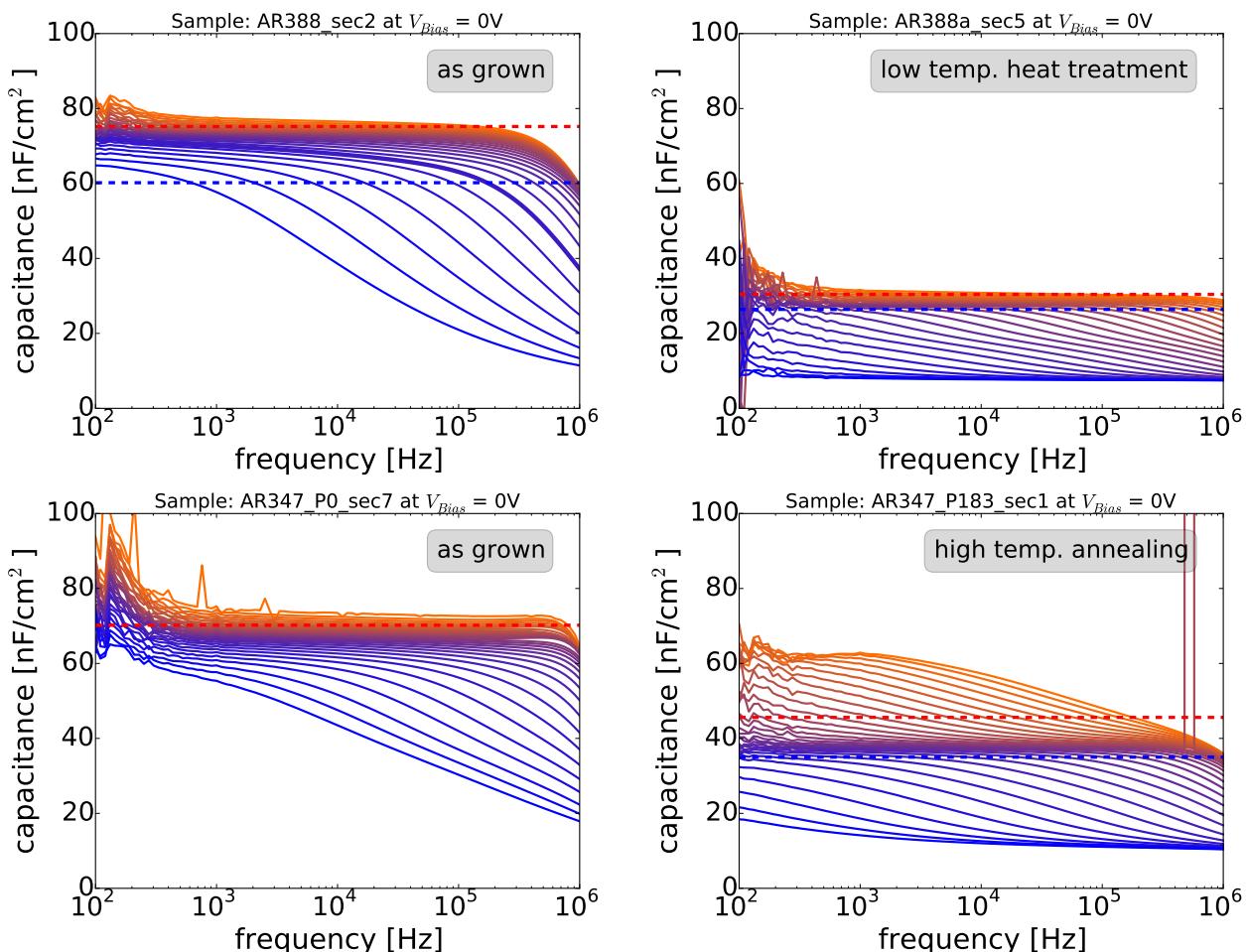

### 3.3.3. Additional heat treatment

Additional to the high temperature co-evaporation process a heat treatment can be applied to the absorber layers. Two different heat treatments were carried out from which finished solar cell devices were characterized by IVT (section 6.3.2) and admittance (section 5.6.2) measurements.

**low temperature heat treatment** This treatment includes an annealing at 180 °C in the PVD chamber, i.e. in vacuum with a base pressure of approximately  $1 \cdot 10^{-8}$  torr. The temperature is slightly below the critical temperature of the order-disorder transition of 200 °C and thus, a bit of ordering is expected after the heat treatment.

**high temperature annealing** The high temperature annealing process for the high temperature co-evaporated absorber layers is the same as for the sequential process described in

### 3. Growth of the CZTSe absorber layer

section 3.2.4. A motivation for an additional high temperature annealing in a Se and SnSe atmosphere is to provide a high Se and SnSe partial pressure at high temperatures, which is not possible in the PVD chamber. Shin *et al.* [83] showed that if the Se partial pressure during annealing is not high enough, PL peaks below the bandgap arise, which might be defect related.

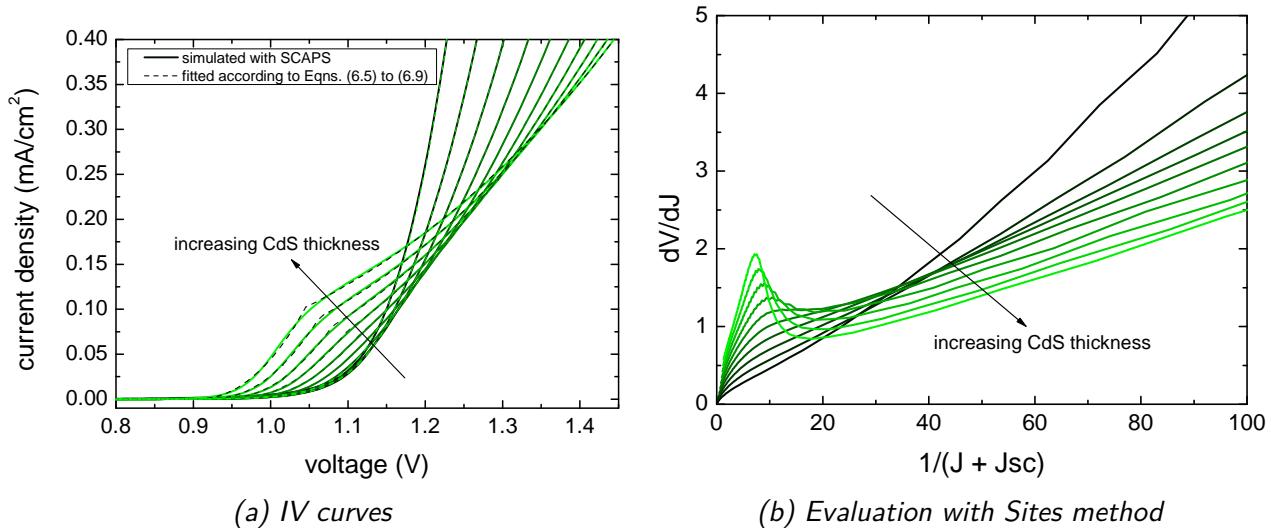

## 3.4. CdS thickness variation

As described in section 2.2.1, the solar cell structure includes a CdS buffer layer with a nominal thickness of 50 nm. As will be shown in section 6.3.1.1 and section 5.7.2, insights about recombination processes and barriers within the heterojunction can be obtained by investigating samples with different CdS buffer layer thicknesses. Different CdS buffer layer thicknesses were deposited on absorbers from one co-evaporation process. It needs to be emphasized that all absorbers came from the same deposition run and are therefore identical except the CdS buffer layer. Also the window layer (i:ZnO/Al:ZnO bilayer) and the Ni/Al grid was processed for all these samples in the same run.

### 3.4.1. Absorber growth

The samples were grown by the standard co-evaporation process described in section 3.3.2. An additional low temperature heat treatment was applied inside the MBE chamber directly after the growth process, i.e. without any air exposure in between. As I will show in section 6.3.2 and have published in Ref. [41] such a heat treatment reduces the doping density significantly and a double capacitance step gets more pronounced<sup>2</sup>. A clear double capacitance step facilitates the evaluation of the admittance data and therefore allows for interpretation of the admittance data based on different CdS buffer layer thicknesses (see section 5.7.2). Additionally, the liquid N<sub>2</sub> cooling of the chamber was maintained throughout the low temperature heat treatment in order to prevent any desorption of elements from the chamber walls onto the absorbers.

### 3.4.2. CdS growth

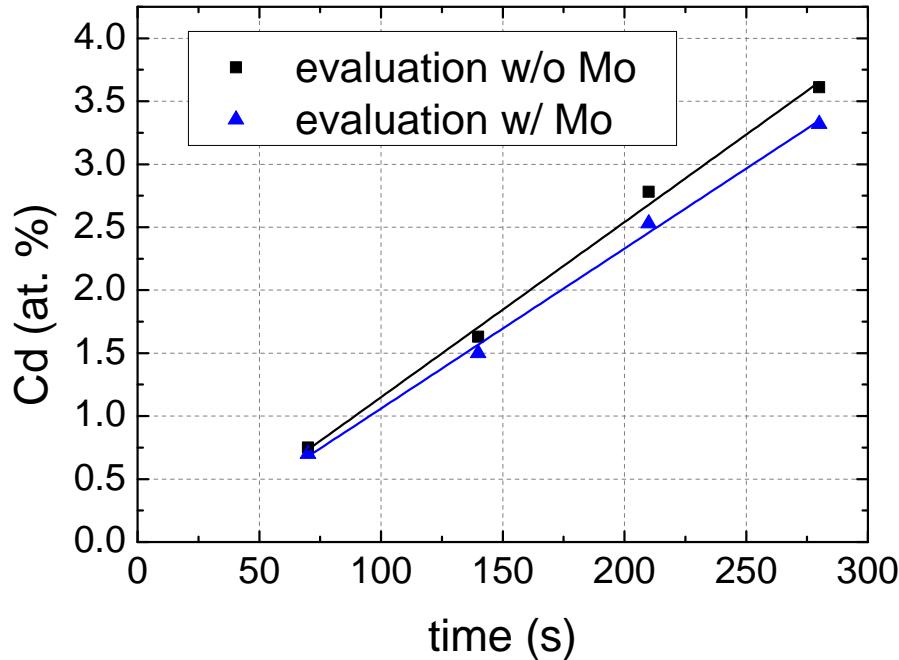

The CdS buffer layer is grown by a chemical bath deposition process following Contreras *et al.* [101]. The deposition of CdS onto the absorber starts as soon as the Thiourea ((NH<sub>2</sub>)<sub>2</sub>CS) is added into the solution of cadmium sulfate (CdSO<sub>4</sub>) and ammonia (NH<sub>3</sub>). From this point on the deposition of CdS takes around 4:40 minutes to obtain a roughly 50 nm thick CdS buffer layer. This procedure with a deposition time of 4:40 (280 s) minutes is in the following referred to "1.0 CdS runs".

The growth of CdS is generally not constant with respect to time. In order to check the deposition rate, CdS was grown on CZTSe absorbers for different time periods between 70 and 280 s. The amount of CdS was then evaluated by EDX measurements. The result is shown in Fig. (3.6) from which it is concluded that the growth rate within this time interval is approximately constant.

---

<sup>2</sup>However, the reduction of the effective doping density was not observed to be as strong as for the samples with air exposure between growth and additional heat treatment

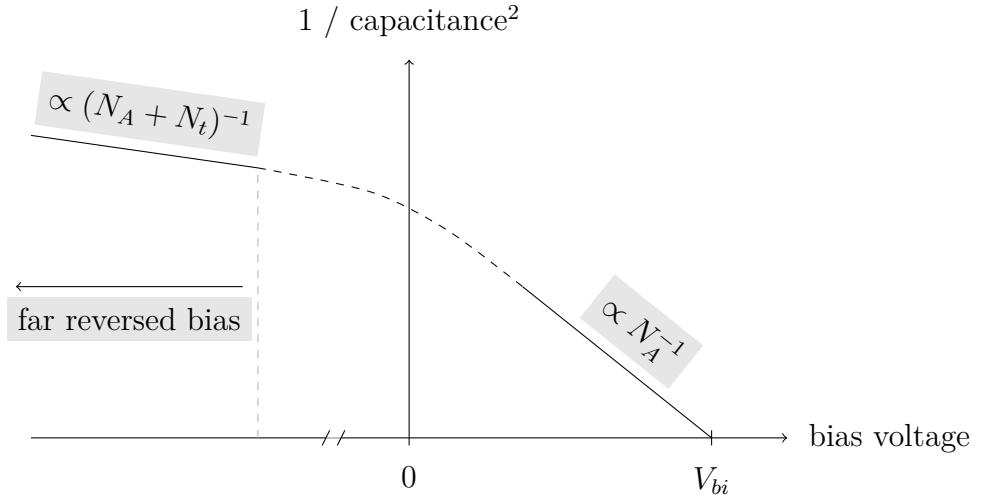

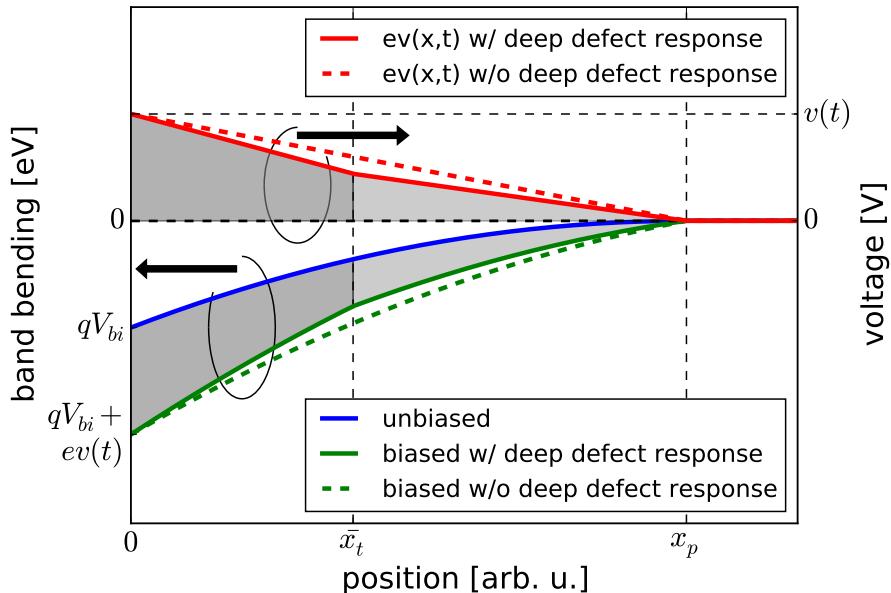

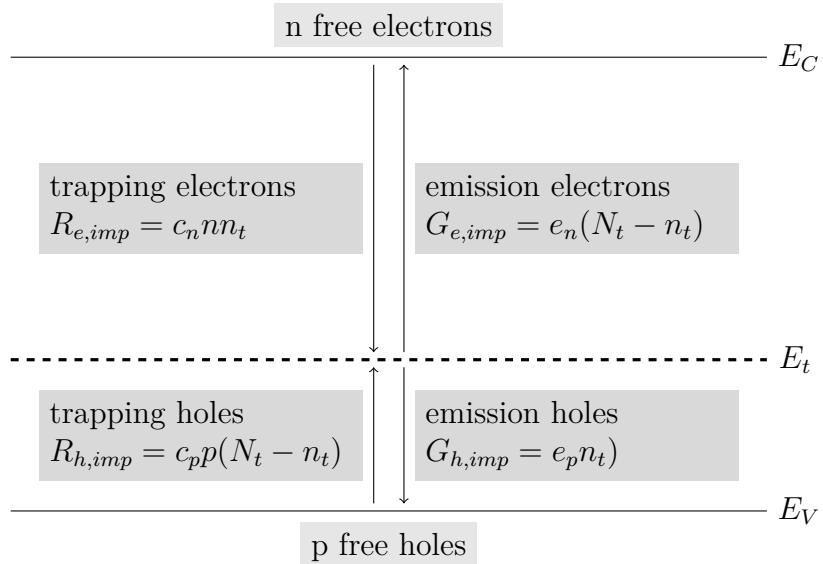

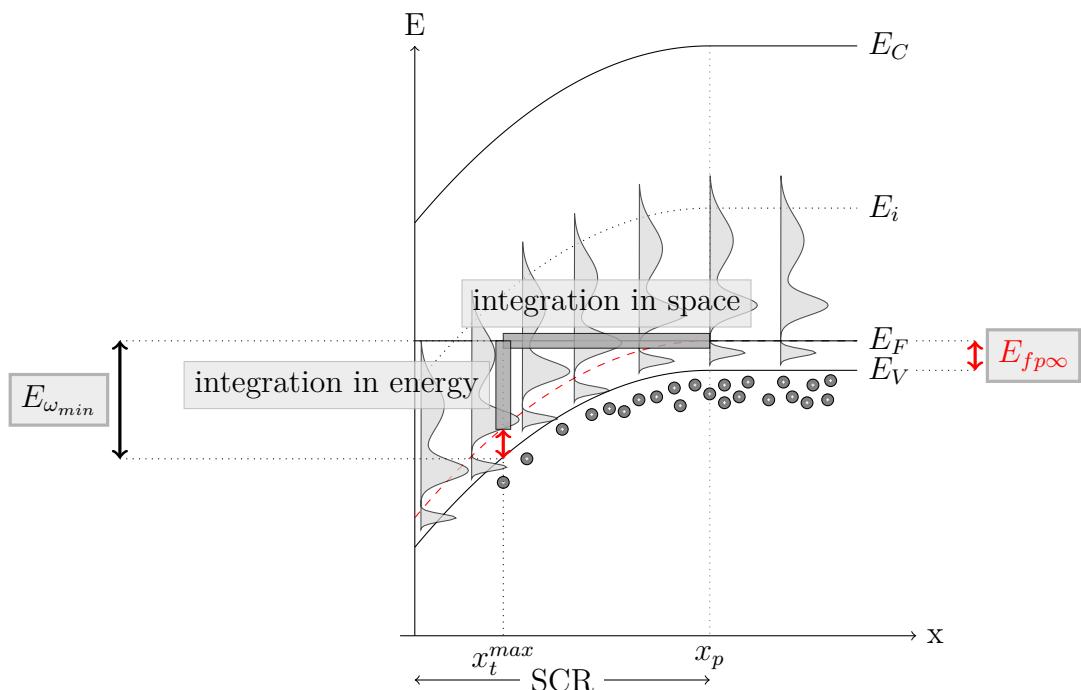

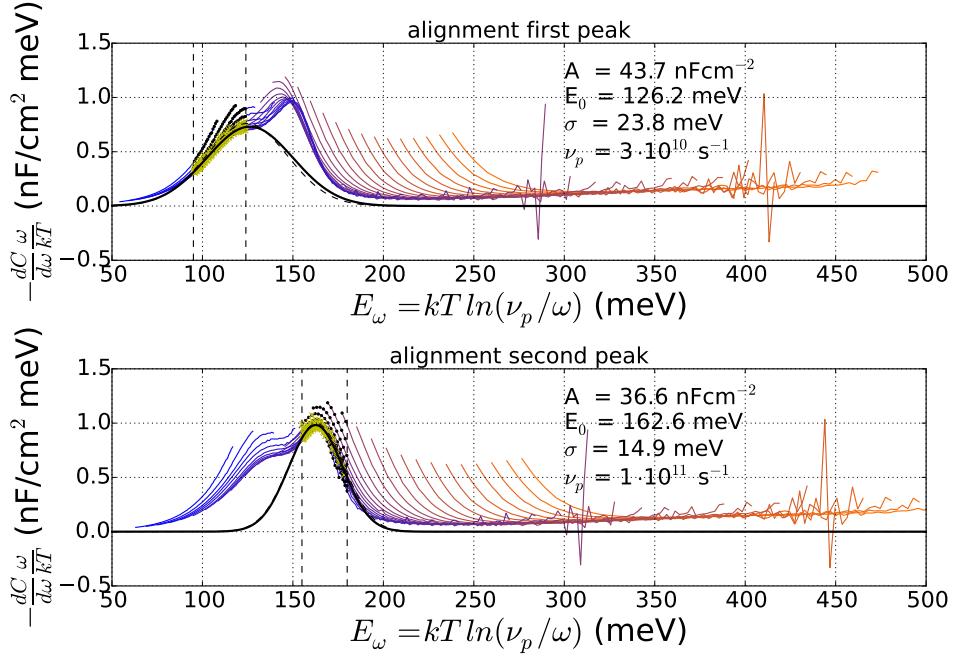

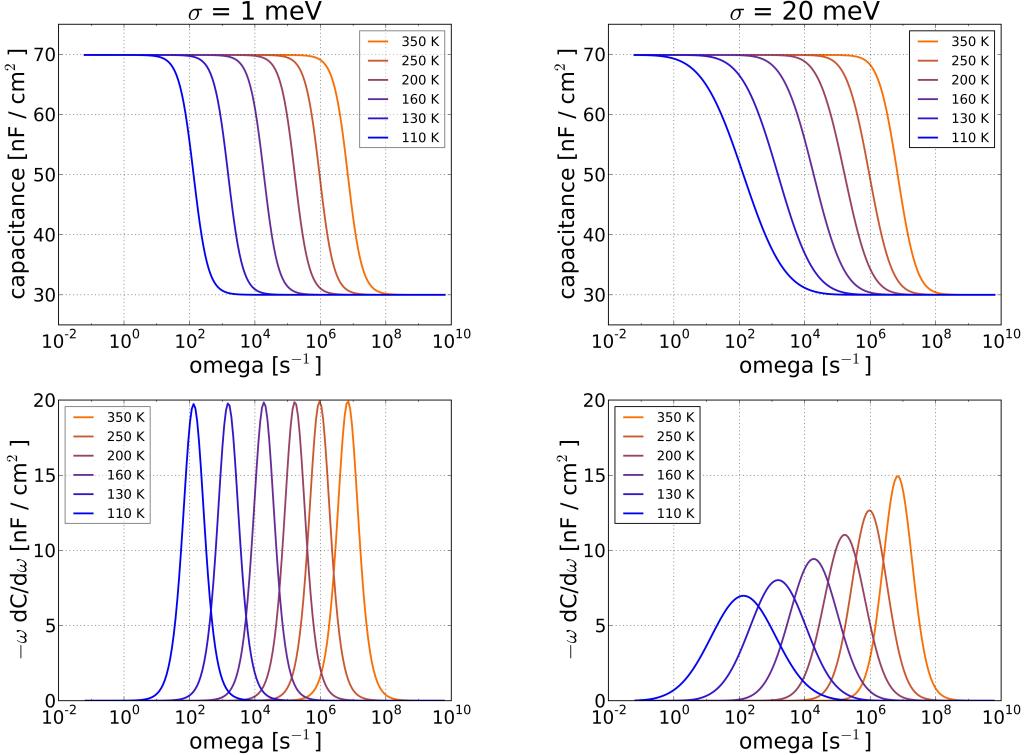

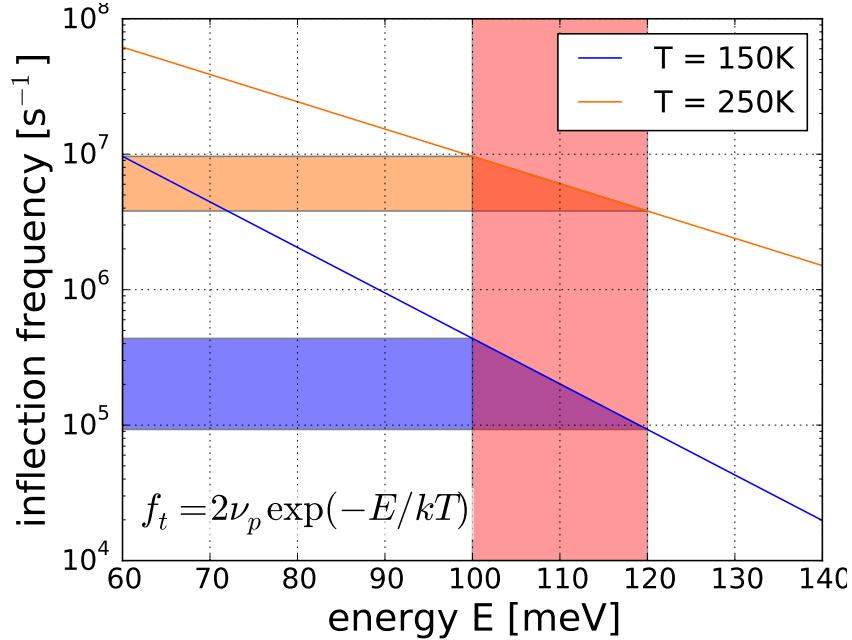

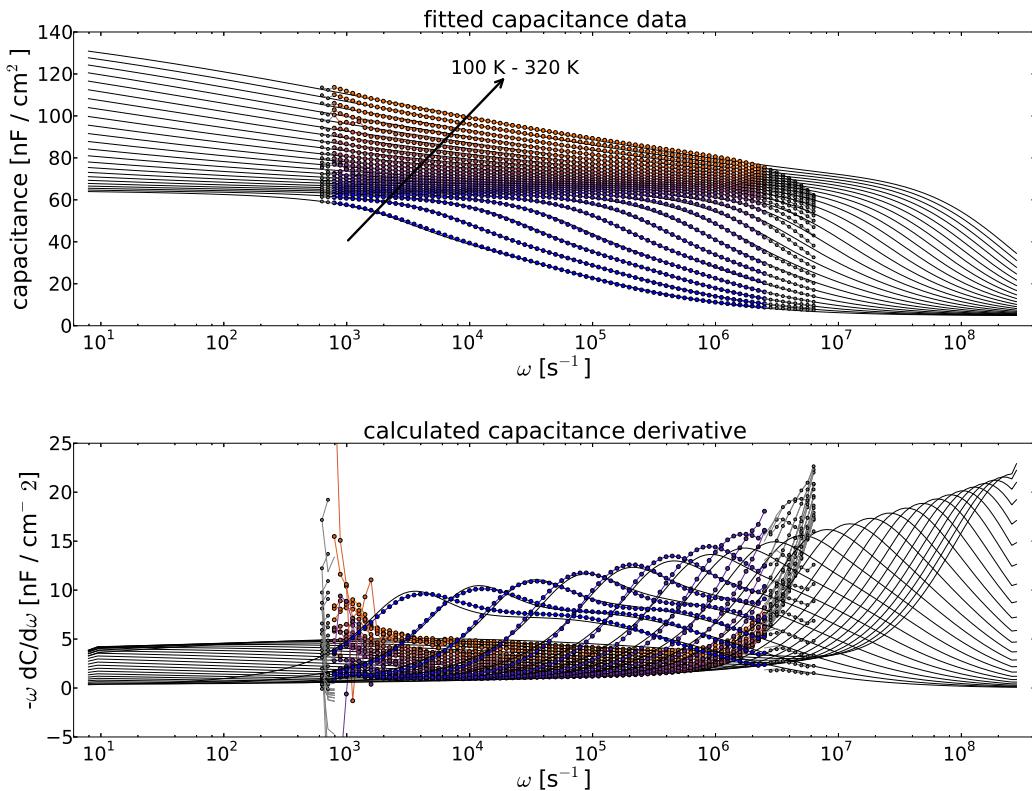

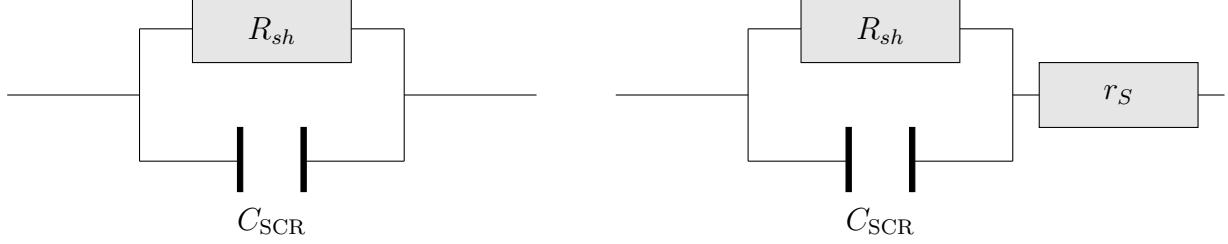

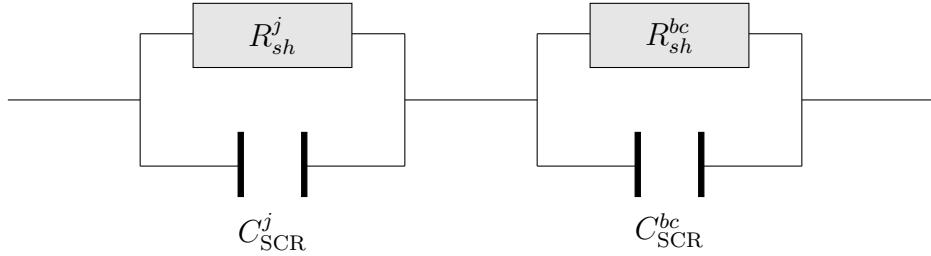

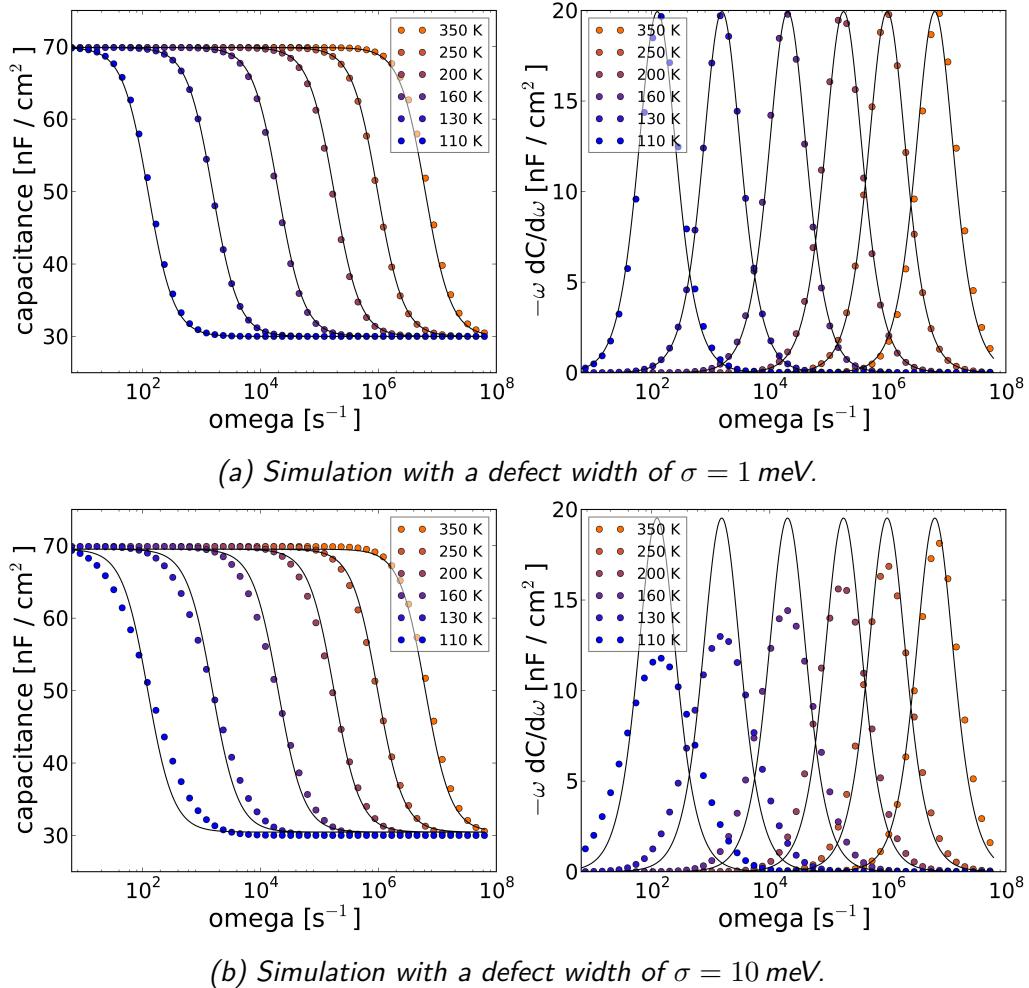

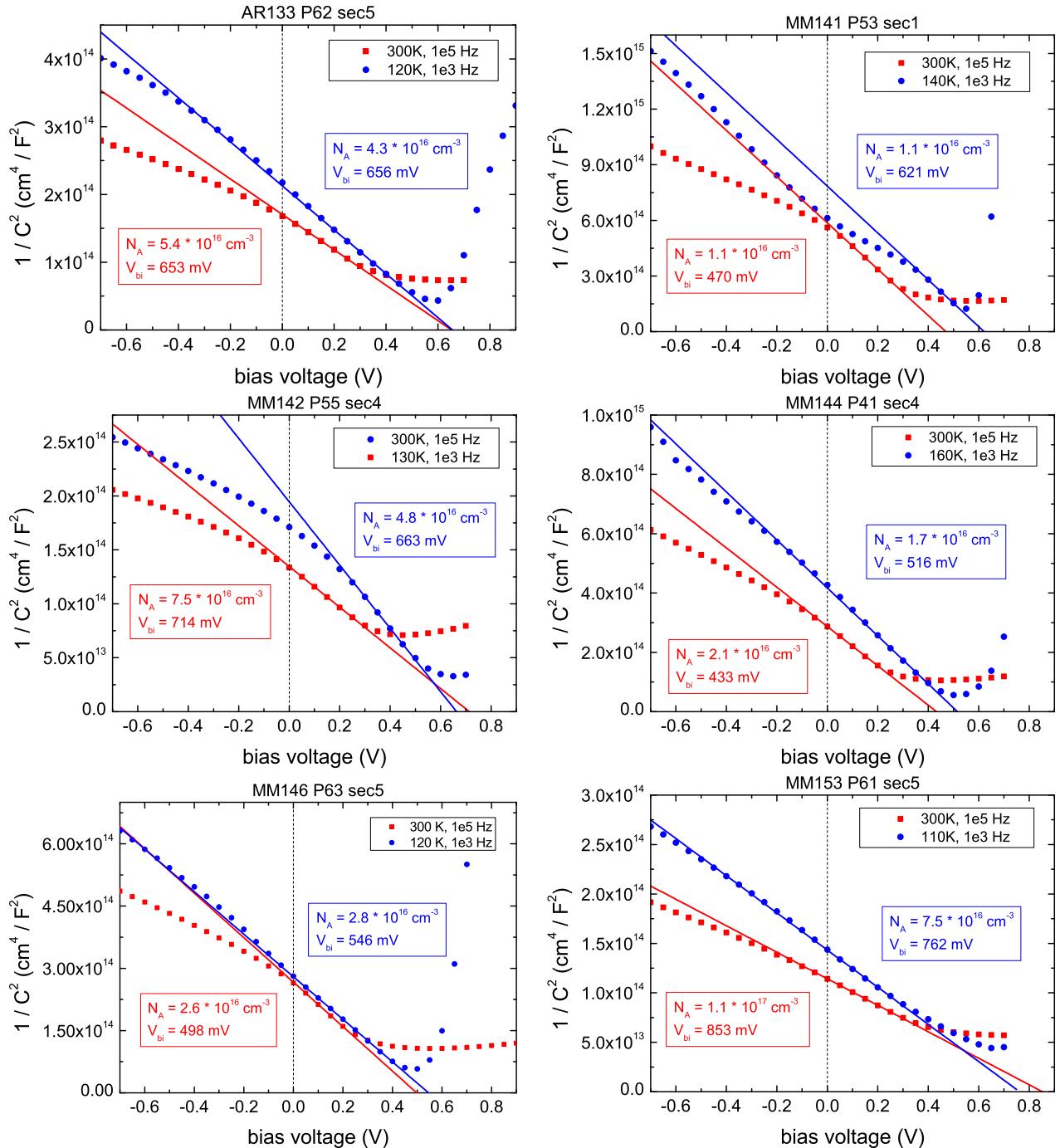

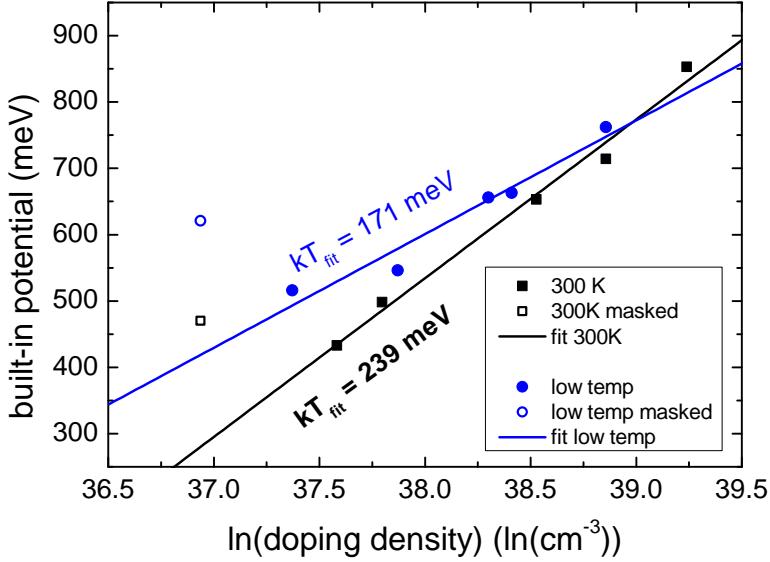

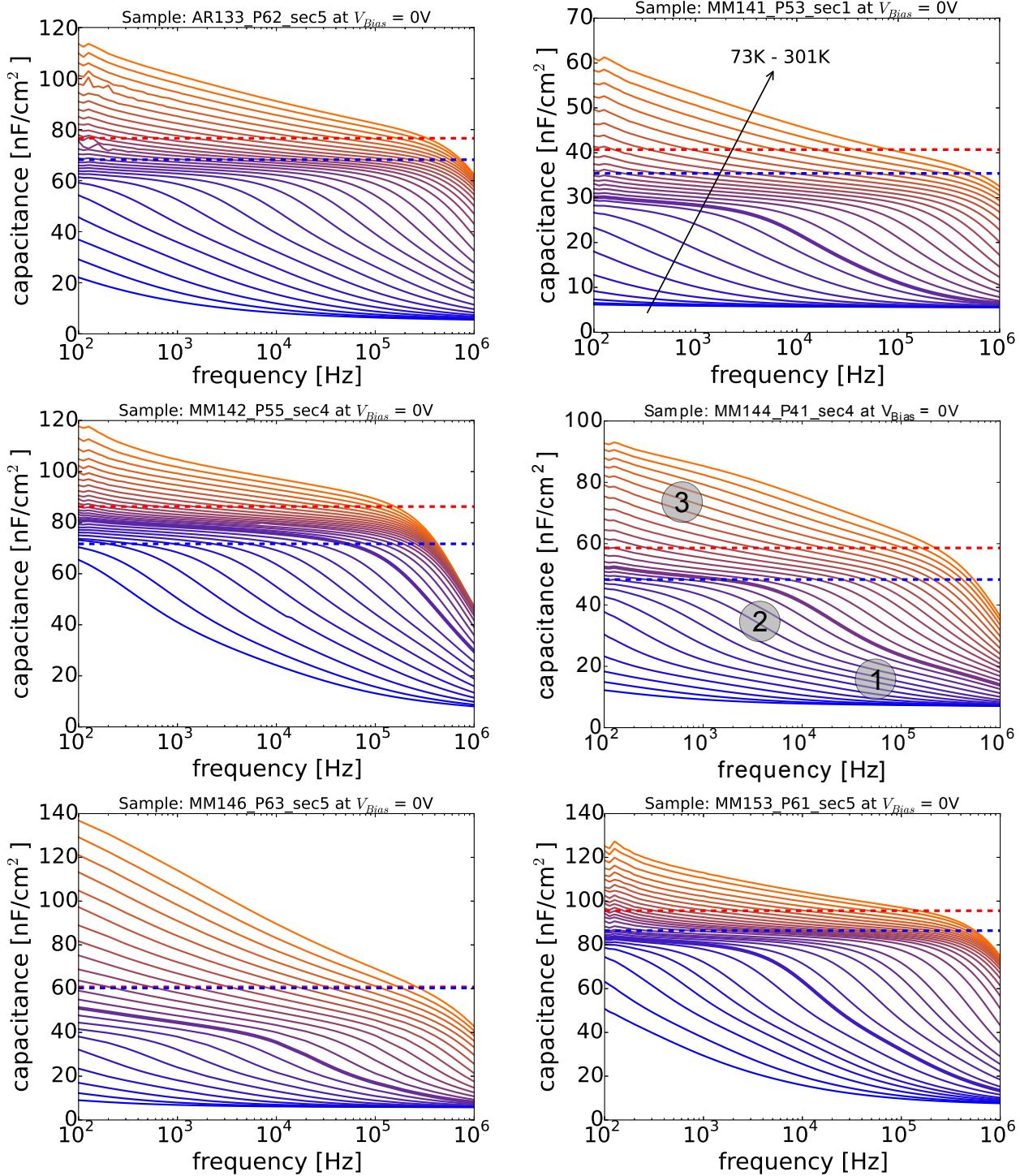

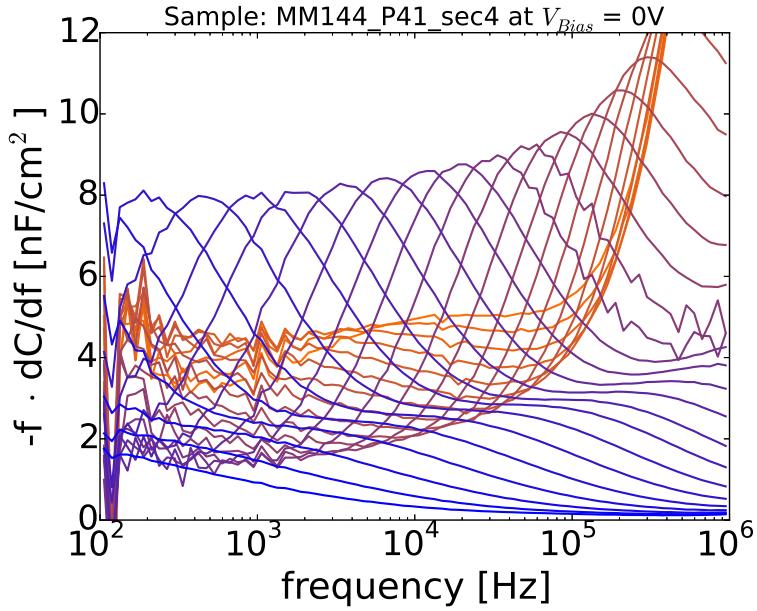

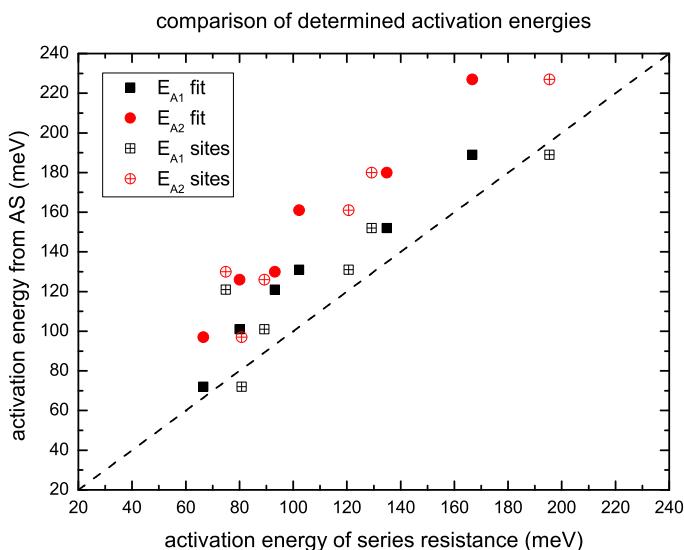

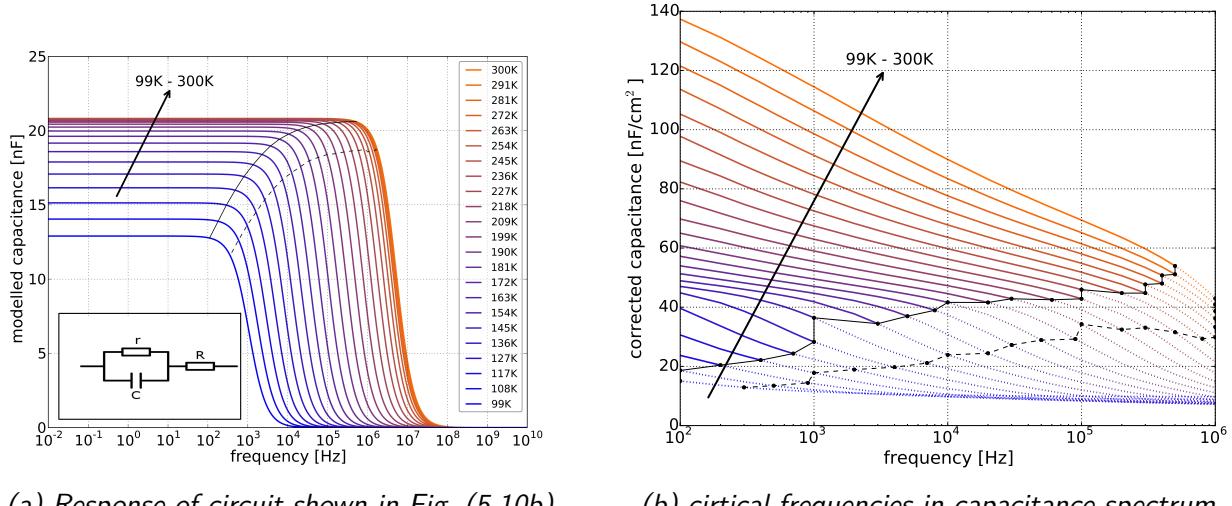

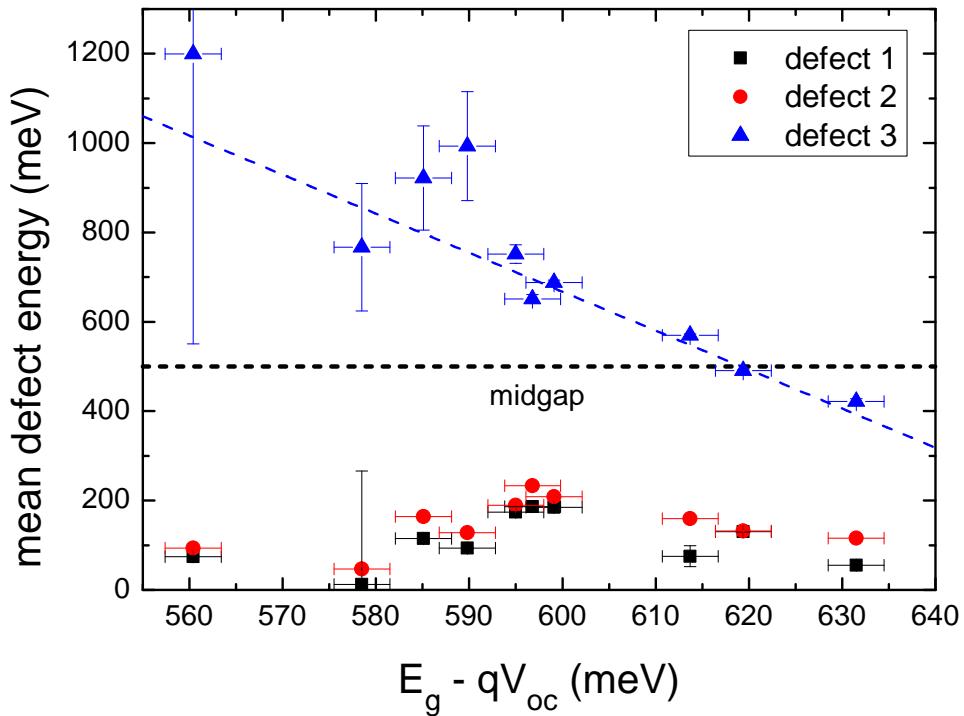

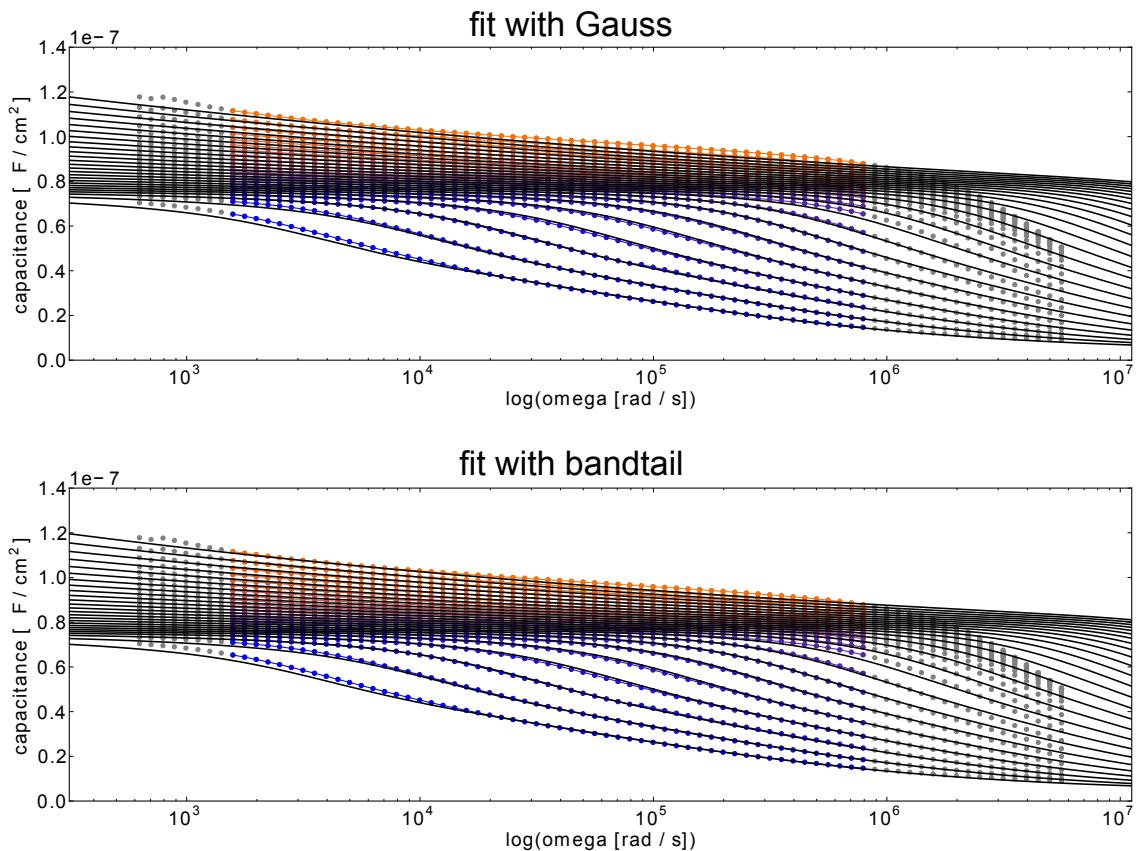

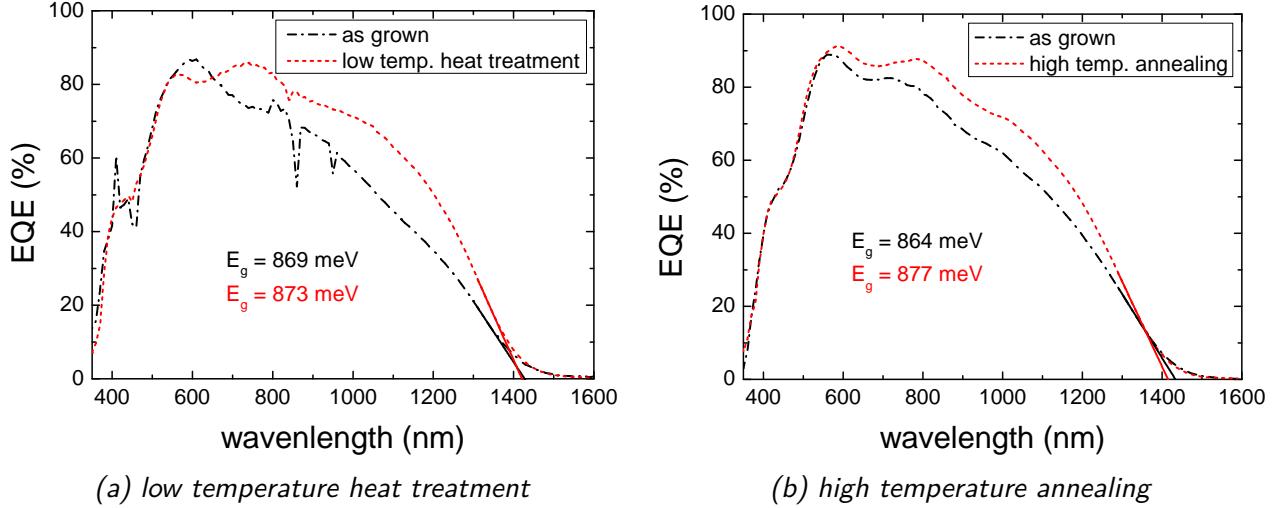

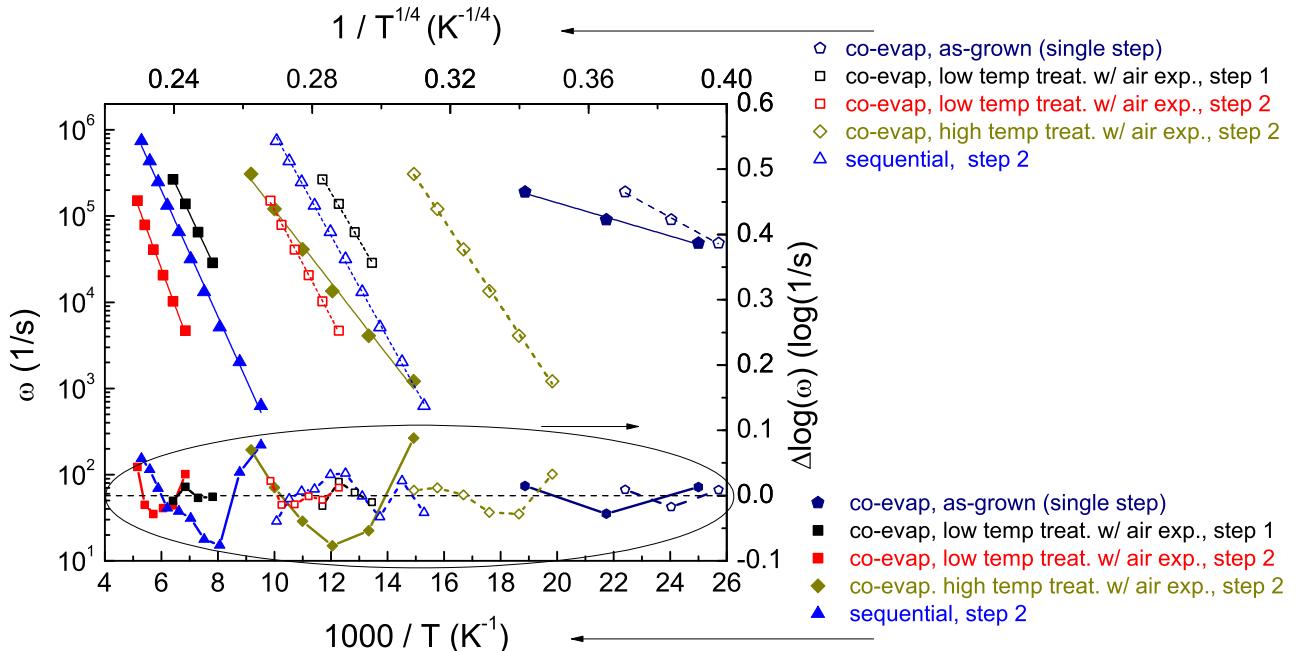

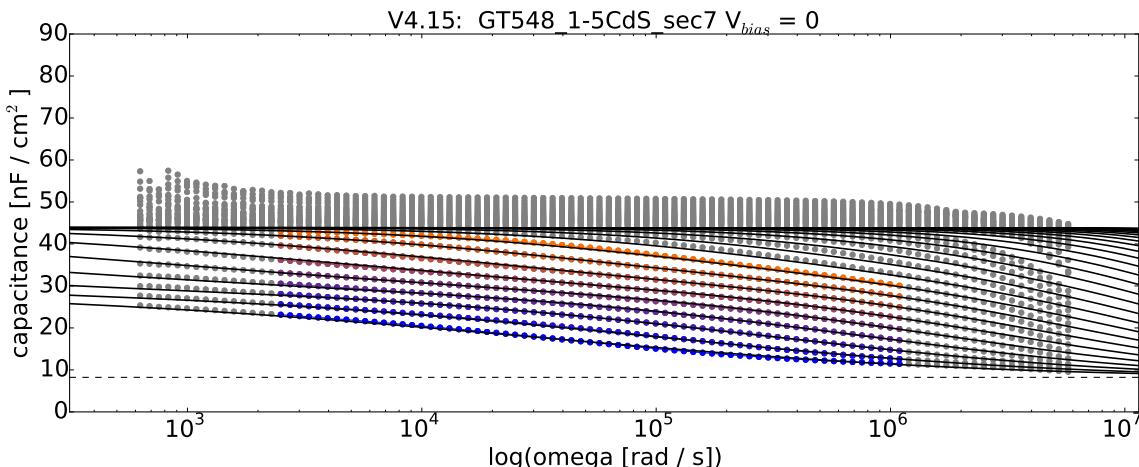

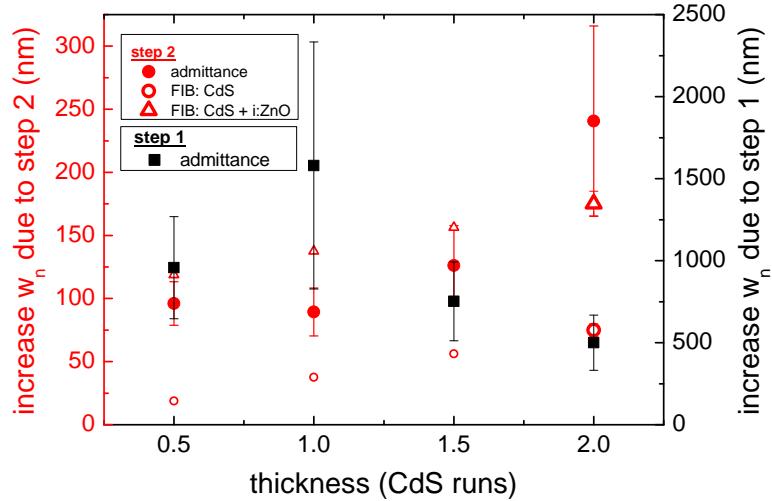

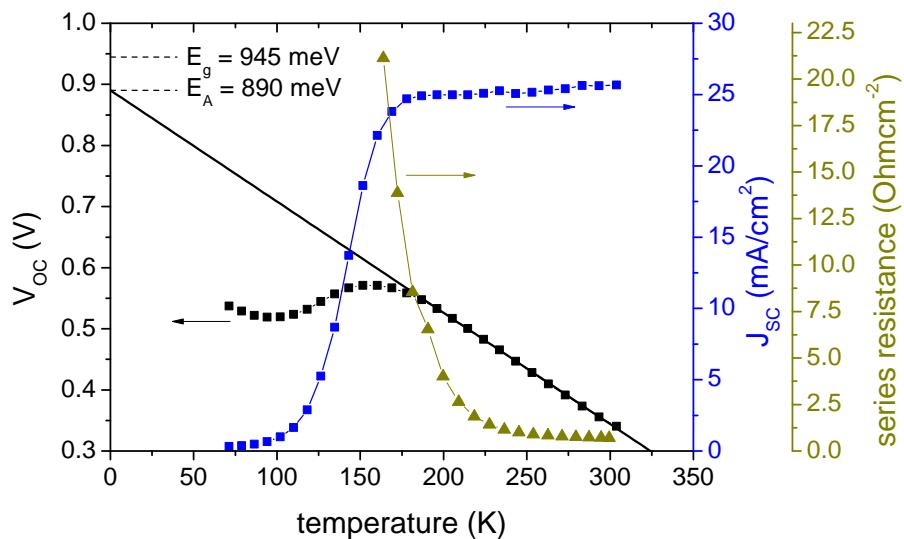

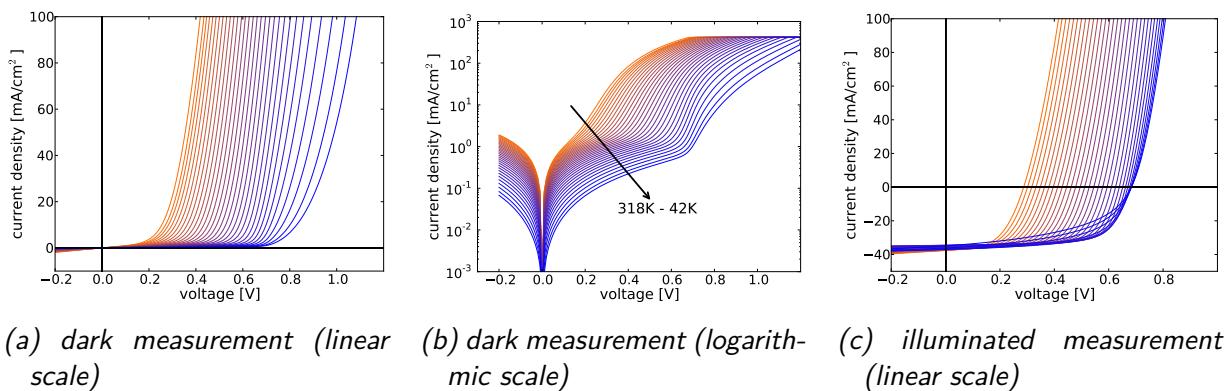

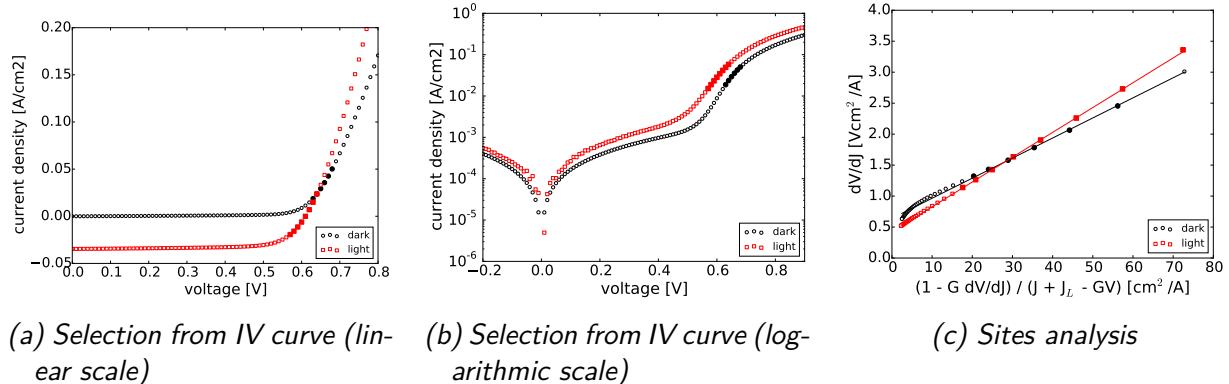

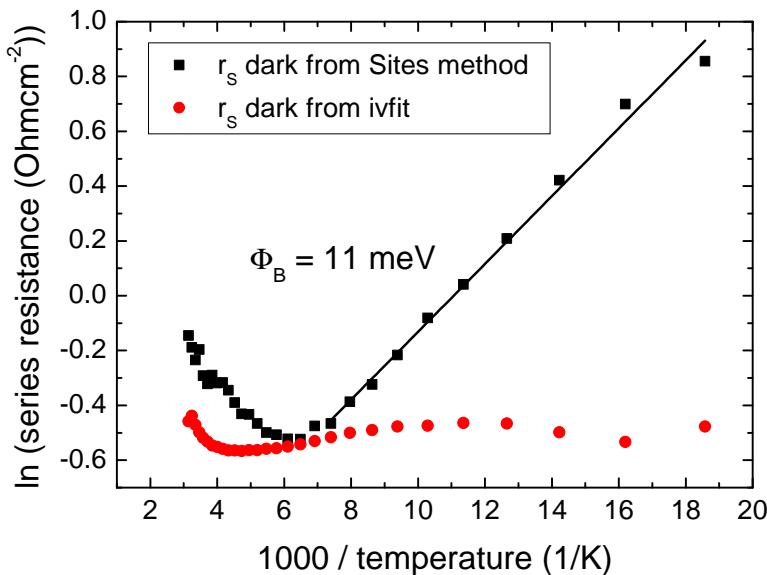

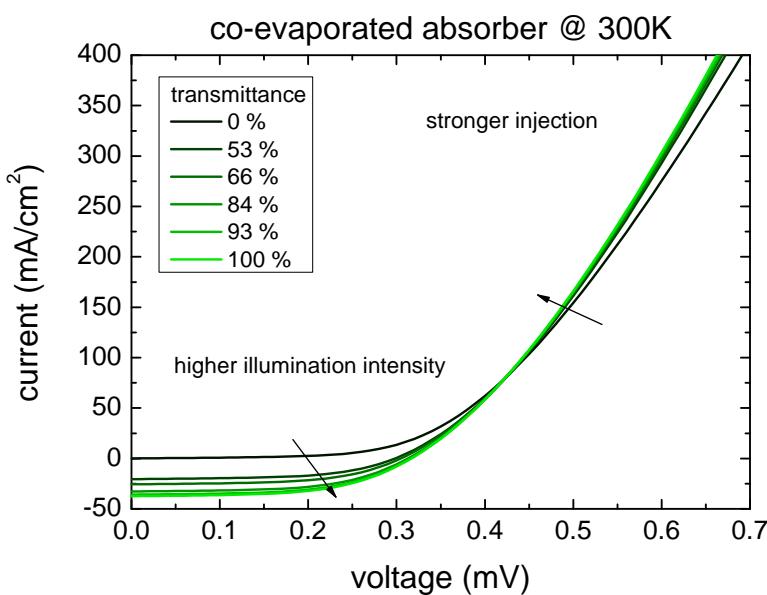

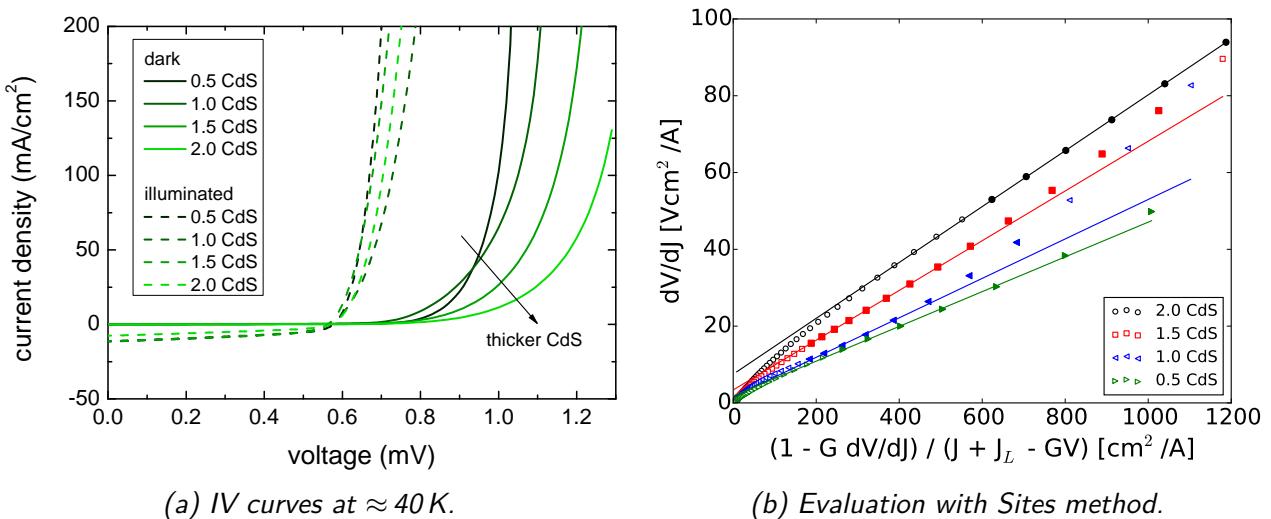

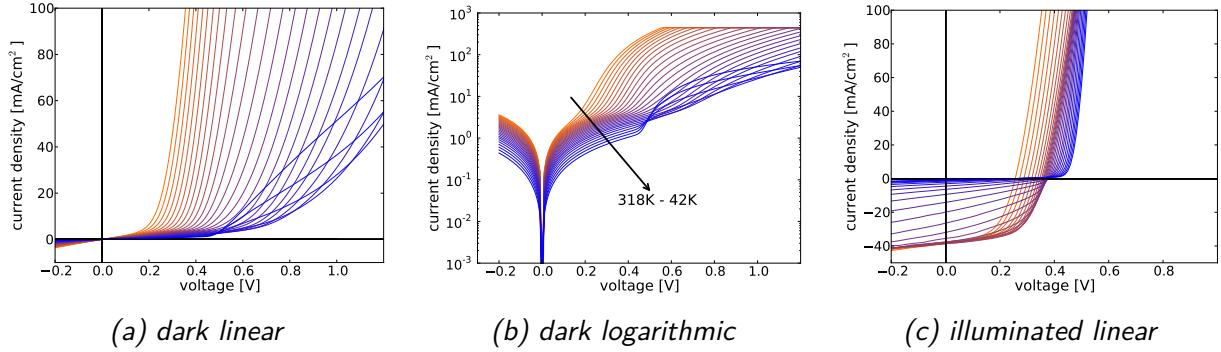

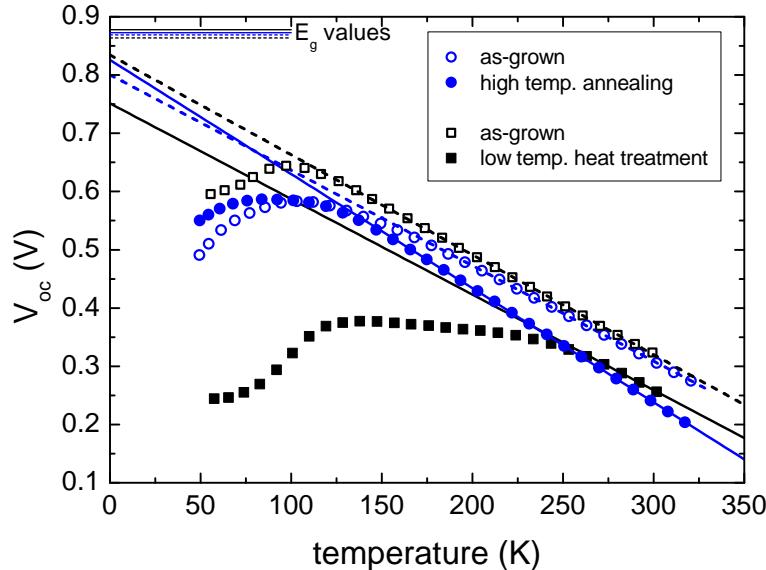

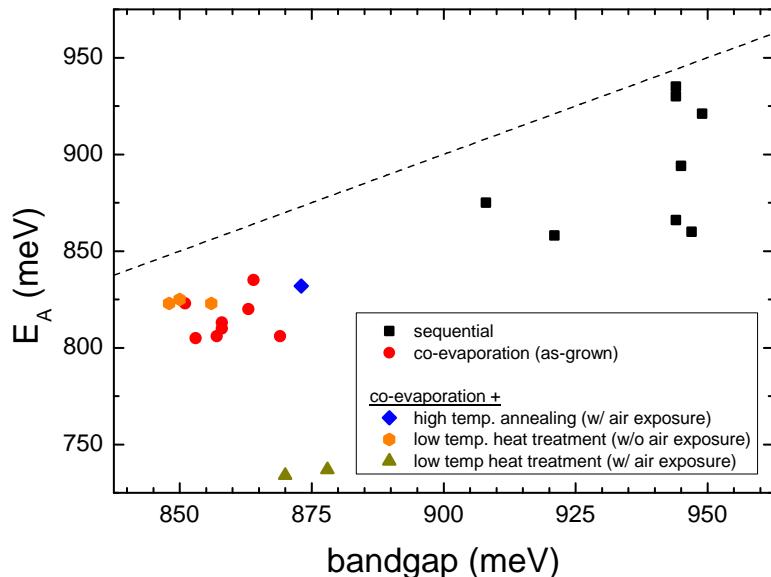

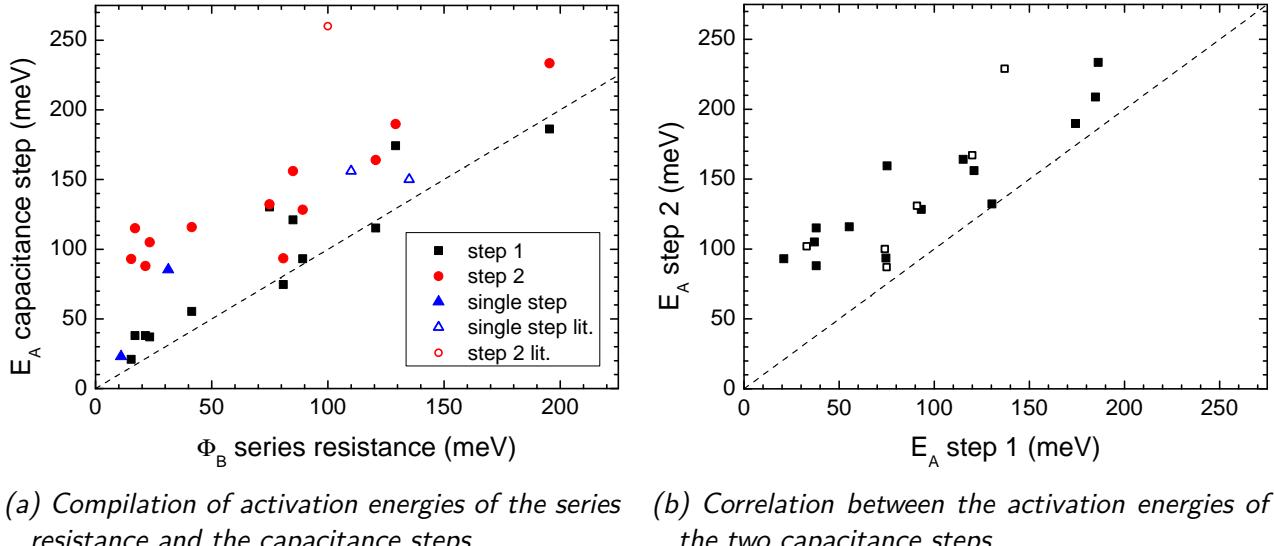

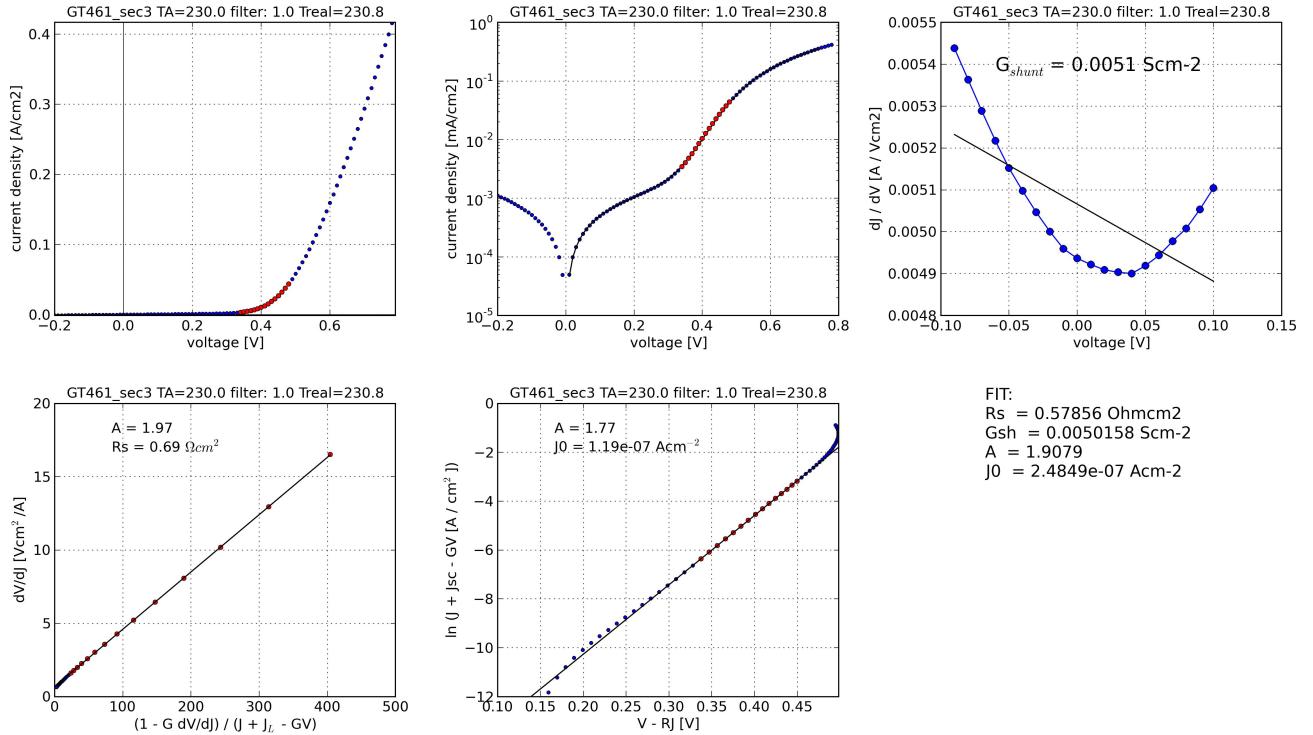

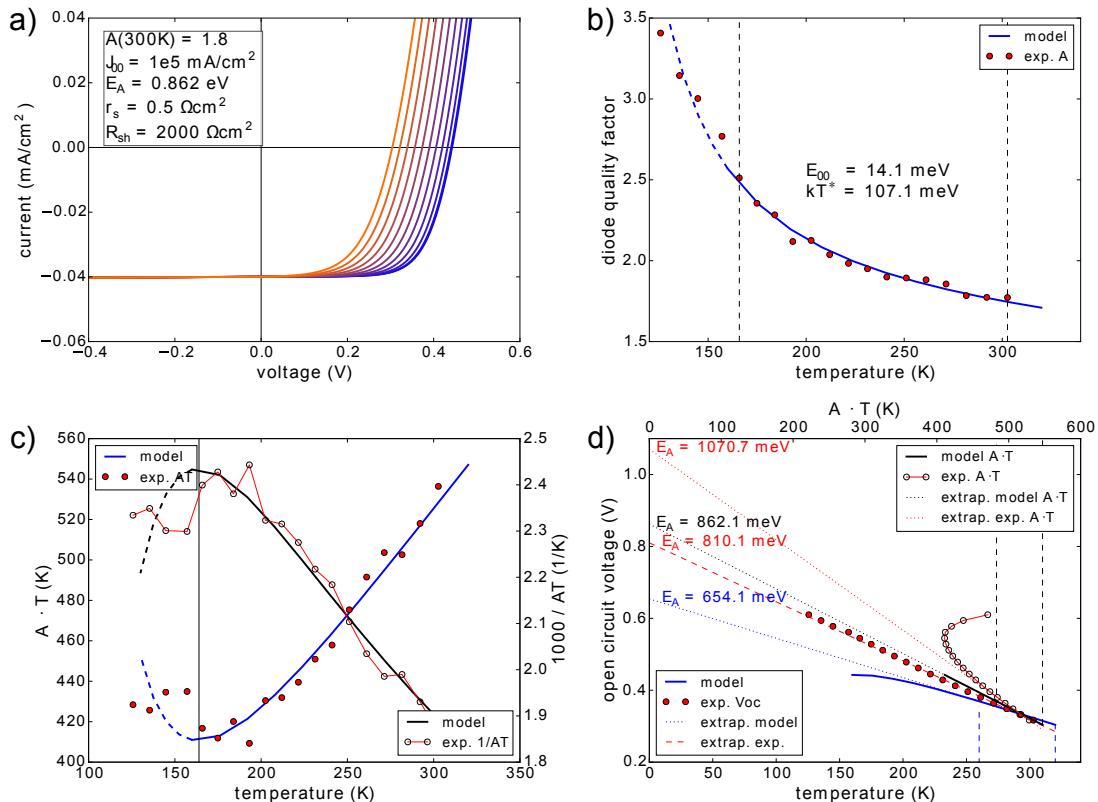

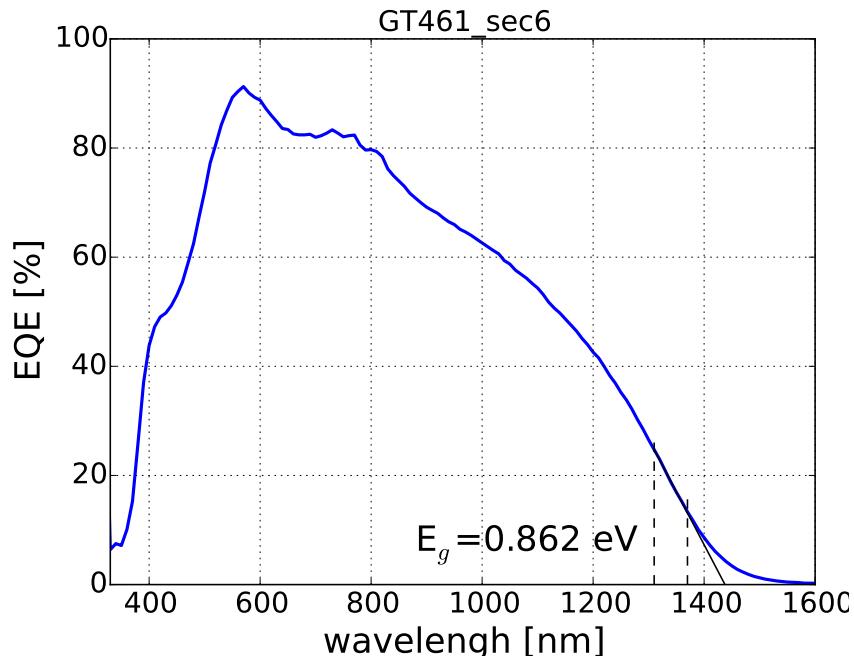

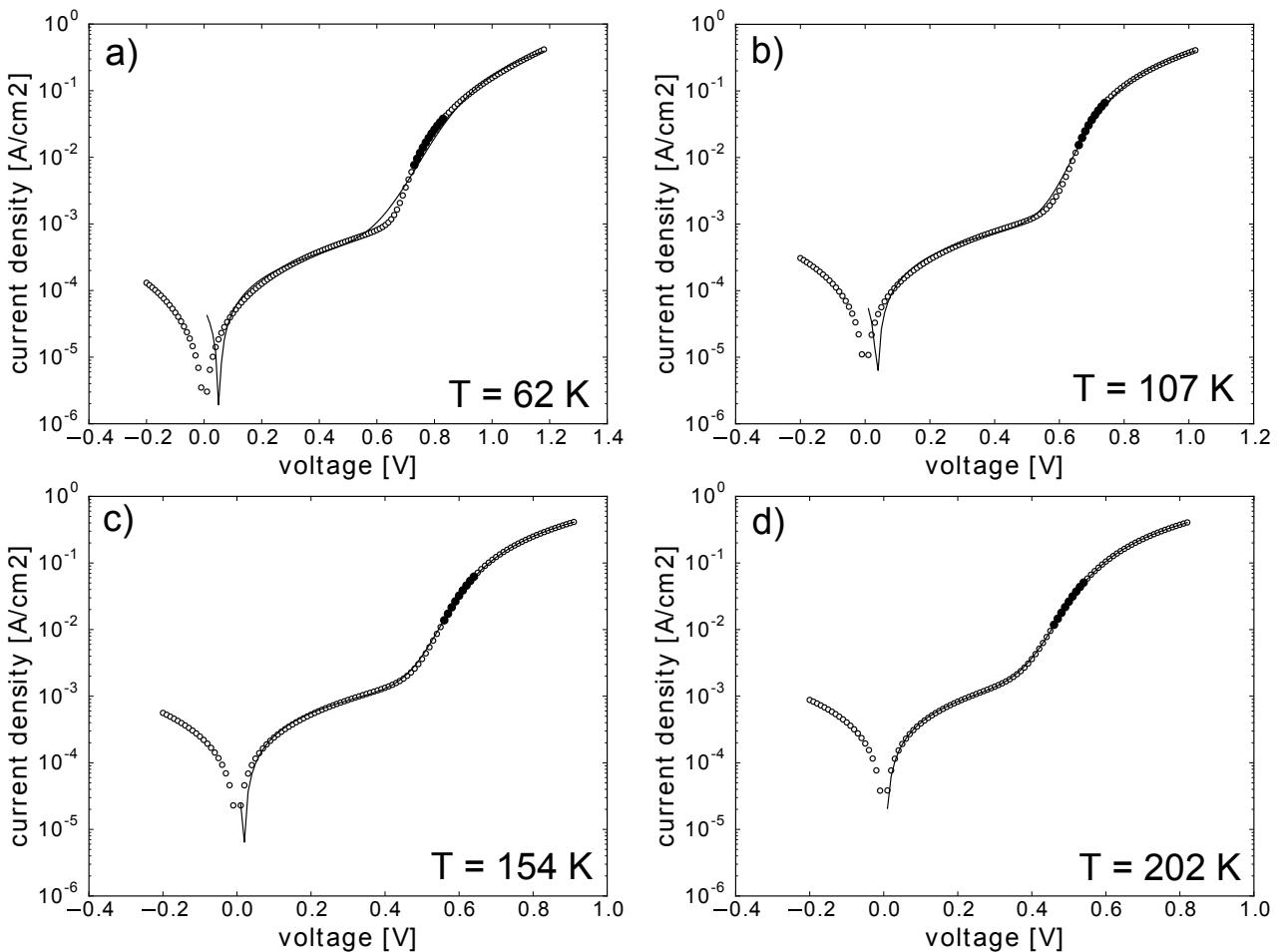

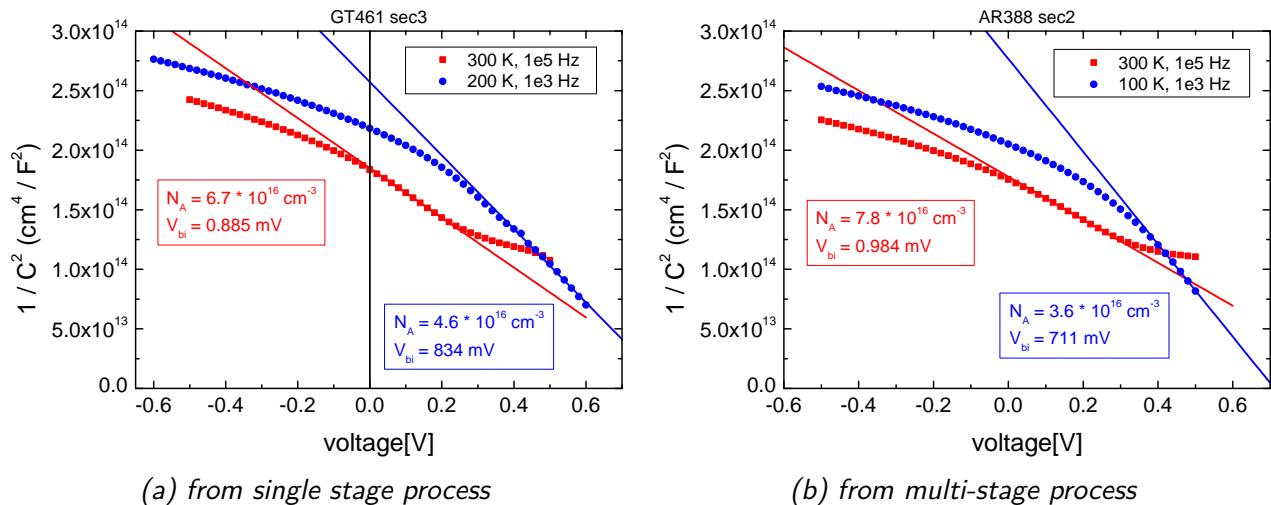

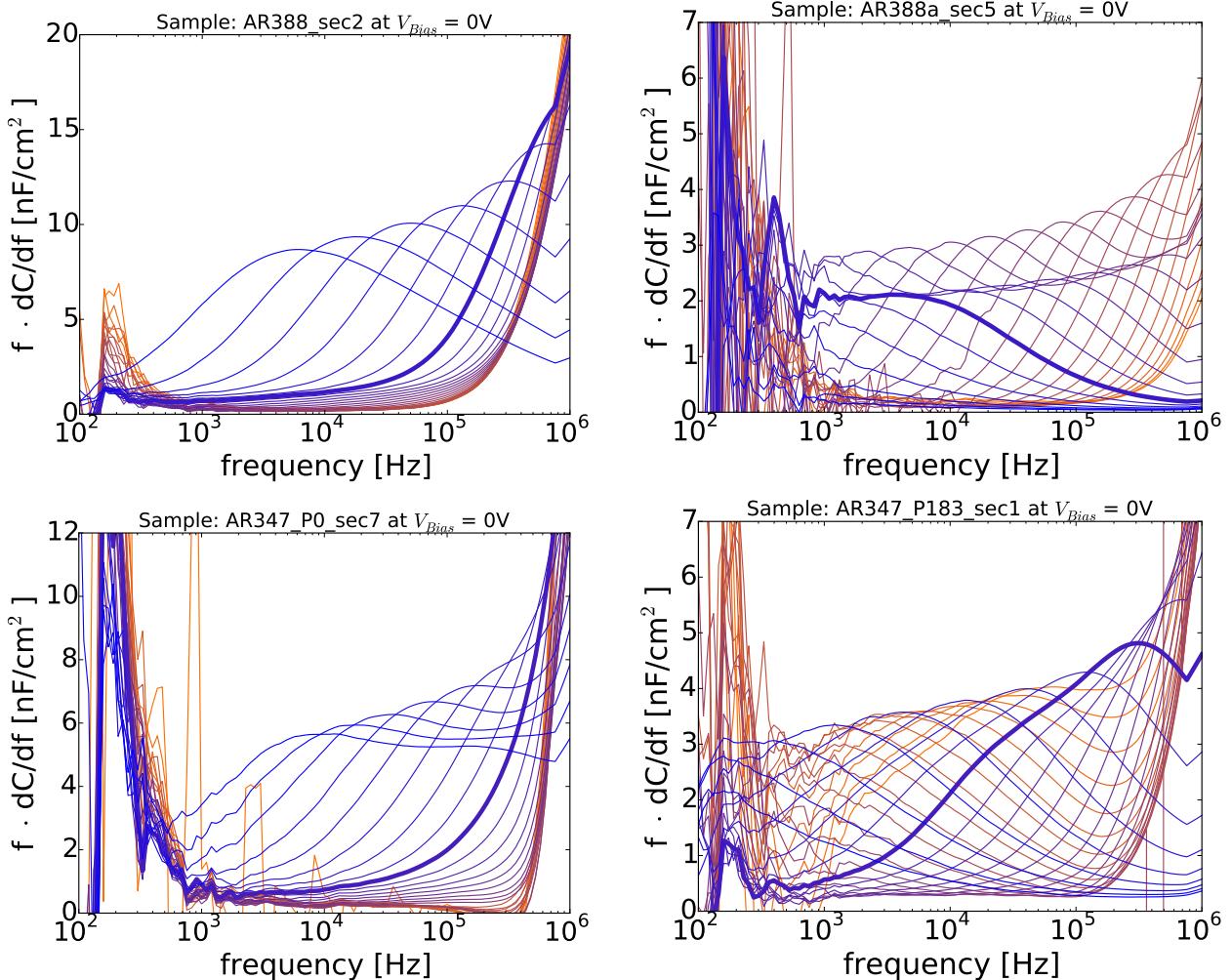

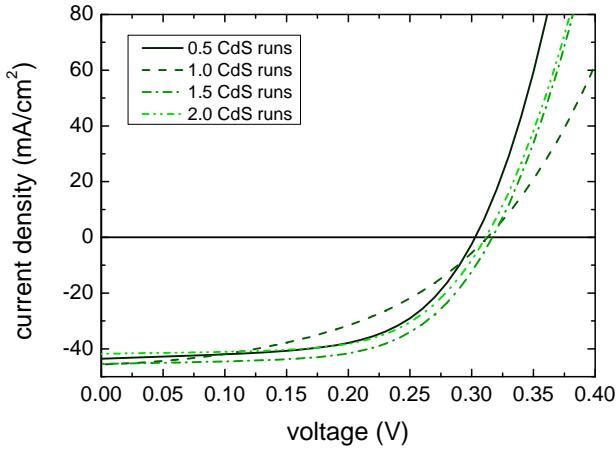

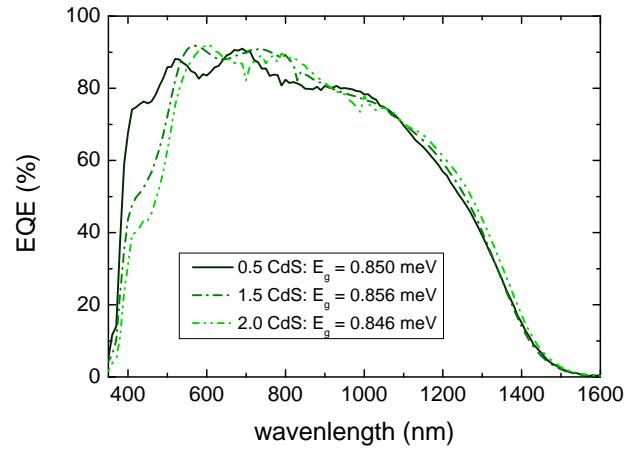

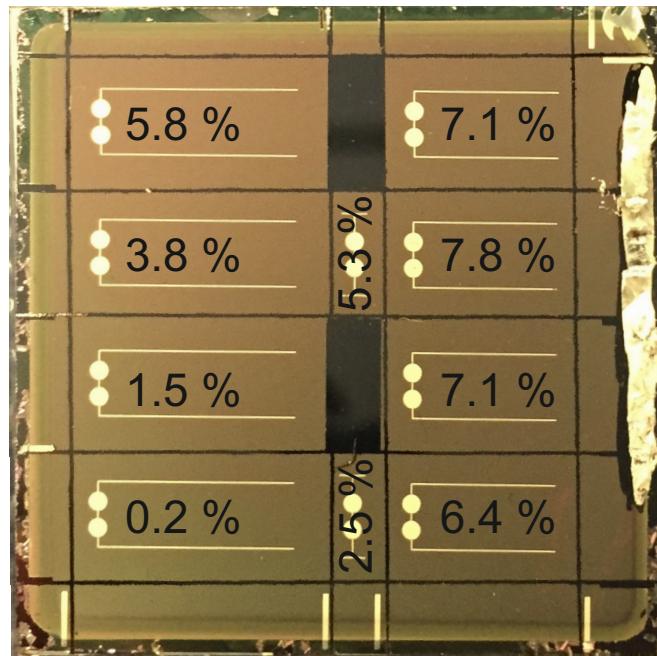

**Figure 3.6.: Evaluation of the CdS thickness by EDX** - Amount of at. % of Cd in the film is evaluated with EDX measurements. As the CdS layer is grown onto CZTSe, the evaluated elements are Cu, Zn, Sn, Se, Cd and Mo (blue triangles). Black circles show the result when the Mo peak is not taken into account for the EDX evaluation. An approximately linear deposition rate with respect to time can be inferred.